PLL и система тактирования R1¶

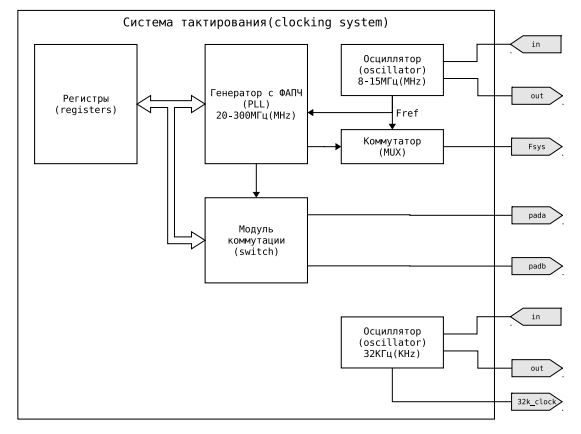

В составе микропроцессора имеется встроенный генератор для формирования системного сигнала тактирования.

Генератор формирует стабильный тактовый сигнал в диапазоне частот от 20 МГц до 300 МГц.

Синтезатор основан на схеме ФАПЧ с целочисленными коэффициентами деления синтезируемой частоты.

Частота опорного сигнала от 8 до 16 МГц.

Возможна работа без задействования встроенного генератора, используя источник внешнего опорного сигнала тактирования.

В качестве источника может быть выбран генератор или кварцевый резонатор.

Для часов реального времени сделан дополнительный частотный домен на 32 КГц.

Хотя блок RTC может работать от внутренней тактовой частоты процессора.

Рассмотрим основные регистры и параметры:

Для управления блоком PLL используются следующие системные регистры:- PLLCR (регистр управления)

- PLLSTR (регистр состояния)

- PLLMCR (регистр управления модулем коммутации)

- R (коэффициент деления опорной частоты) - биты RCNT регистра PLLCR

- N (коэффициент деления внутреннего генератора) - биты NCNT регистра PLLCR

- K (коэффициент деления выходного делителя) - биты MXVCO регистра PLLCR

При выборе коэффициентов необходимо, чтобы они соответствовали условиям работоспособности блока.

1) 1 МГц < Fcmp < 16 МГц

2) 20 МГц < Fvco < 340 МГц

Fcmp = (1/R)*Fref

Fvco = N*(1/R)*Fref

Fout = (1/K)*Fvco

Выходная частота рассчитывается по следующей формуле: Fout = Fref*N*(1/R)*(1/K)

Где Fref - опорная частота (на текущей отладочной плате компании LDM-Systems 8 МГц)

Fcmp - частота сравнения на входе фазо-частотного детектора

Fvco - частота внутреннего генератора, управляемого напряжением (ГУН)

Fout - выходная частота

Включение после сброса или подачи питания:

- Установить биты PLLCR (NCNT) и PLLCR (RCNT) в нужное значение

- Установить бит PLLCR (EN) в "1"

- Дождаться установки бита PLLSTR (LOCK) в "1"

- Переключиться на нужную частоту установкой битов PLLCR (MXVCO)

- Установить третий бит MXVCO, т.е. PLLCR [11] в "0" , чтобы переключиться на Fref

- Изменить биты PLLCR (NCNT) и PLLCR (RCNT)

- Установить третий бит MXVCO, т.е. PLLCR [11] в "1" , чтобы переключиться на новую частоту

- Установить третий бит MXVCO, т.е. PLLCR [11] в "0" , чтобы переключиться на Fref

- Дождаться установки бита PLLSTR (REFACTIVE) в "1"

- Установить бит PLLCR (EN) в "0"

Примечание: Вместо действия [Дождаться установки бита PLLSTR (LOCK) в "1"]

можно подождать 1 миллисекунду.

Рассмотрим пример:

Опорная частота 8 МГц. Требуется выходная частота 30 МГц.

1)Пусть R = 2, K = 4.По формуле для расчёта Fout находим, что N = 30.

Тогда на основании пункта "6.0.3 Таблицы выбора коэффициентов R, N, K" Руководства по эксплуатации R1

находим значения битов RCNT и NCNT:

RCNT = 100 (бинарный формат)

NCNT = 11010 (бинарный формат)

Выставляем 15-бит разрешения работы (En) регистра PLLCR.

В итоге получаем значение 0xC01A.

2)Ожидаем установки бита Lock в регистре PLLSTR

3)На основании пункта "6.0.3 Таблицы выбора коэффициентов R, N, K" Руководства по эксплуатации R1

находим значения битов MXVCO:

MXVCO = 1101 (бинарный формат)

Получаем значение регистра PLLCR = 0xCD1A.

4)Проверяем условия:

а) 1 МГц < Fcmp = 4 < 16 МГц, верно

б) 20 МГц < Fvco = 120 < 340 МГц, верно

Полный пример перехода на частоту в 30 МГц на ассемблере:

;переход на частоту 30МГц pll_30: getl 0xC01A setl #PLLCR, @1 jmp pll_30_lock complete pll_30_lock: getl #PLLSTR getl 1 and @1, @2 je @1, pll_30_lock jne @2, pll_30_set complete pll_30_set: getl 0xCD1A setl #PLLCR, @1 jmp pre_reconf complete

Этот же пример на Си:

void asm_set_PLL(unsigned char RCNT, unsigned char NCNT, unsigned char MXVCO, unsigned char Enable); main() { //переход на частоту 30МГц asm_set_PLL(0x4, 0x1A, 0xD, 1); }

Примечание: для расчета коэффициентов PLL у нас разработана специальная утилита, которая будет доступна на сайте для расчета коэффициентов онлайн.