# USER MANUAL

Multicellular processors: MCp042P200102-LQ256 MCp042R100102-LQ256

#### Abstract

MCp042P200102/MCp042R100102 microprocessor includes a multicellular CPU core, which is the first processor core with a radically new (post-Neumann) multicellular architecture developed in Russia. Multicellular processor is designed for a wide range of control tasks and digital signal processing in applications that require minimum power consumption and high performance. Given multicellular processor consists of 4 cells (coherent processing units) combined by intellectual commutation environment. MCp042R100102 has dynamically reconfigurable core. Cells can be distributed among tasks according with algorithm inside firmware. Wherein any part of code can be processed by any number of cells at any combinations. Core of MCp042P200102 can process only one task at one time.

#### **Features:**

- Cell amount -4

- Processor word 32/64 бита

- DM 128KiB (4\*4K\*64)

- PM 128KiB (4\*4K\*64)

- FPU SP/DP (in each cell)

- Clock frequency 150 MHz

- Processor performance 24 MFLOPS/MHz;

#### General characteristics:

- Package LQFP-256

- Operation environment (-60  $\ldots$  +125°C)

- Maximum power consumption:

- core 0.6Wt at 100MHz

- GPIOs 80мВт

- Supply voltage (separate): cores 1,8V, peripheral - 3,3V

#### **Peripherals:**

- 2 SPI interfaces with slave devices' selector (in "master" mode)

- 4 UART with FIFO for receive-transmit

- 2 I2C interfaces (one "master" and one "slave")

- I2S interface (one "master", receive data)

- Ethernet MAC controller 10/100Mb/s

- USB 2.0 FS (device), external interface ULPI

- RTC with calendar

- 4 GP timers

- 6 GPIO, total amount of input-output ports

166

- PWM controller with 4 channels

- WDT

- ADC(48ksps, 16bit, 8ch)

- DAC(125ksps, 12bit, 2ch)

# Contents

| <ul> <li>2 Description <ol> <li>General technical characteristics</li> <li>MP structure</li> </ol> </li> <li>3 Central processor unit <ol> <li>Registers</li> </ol> </li> <li>4 Memory organization <ol> <li>Memory switch</li> <li>Memory switch</li> <li>Memory switch</li> </ol> </li> <li>5 Clock system </li> <li>6 Debugging system </li> <li>7 Peripheral devices</li> </ul> | 5<br>5 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| <ul> <li>2.2 MP structure</li></ul>                                                                                                                                                                                                                                                                                                                                                 | 6      |

| <ul> <li>3 Central processor unit <ul> <li>3.1 Registers</li> <li>4 Memory organization</li> <li>4.1 Memory map</li> <li>4.2 Memory switch</li> <li>4.3 Data transaction controller (DTC)</li> </ul> </li> <li>5 Clock system</li> <li>6 Debugging system</li> </ul>                                                                                                                | 6      |

| <ul> <li>3.1 Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                    | 7      |

| <ul> <li>4 Memory organization <ul> <li>4.1 Memory map</li> <li>4.2 Memory switch</li> <li>4.3 Data transaction controller (DTC)</li> </ul> </li> <li>5 Clock system</li> <li>6 Debugging system</li> </ul>                                                                                                                                                                         | 9      |

| <ul> <li>4.1 Memory map</li></ul>                                                                                                                                                                                                                                                                                                                                                   | 10     |

| <ul> <li>4.2 Memory switch</li></ul>                                                                                                                                                                                                                                                                                                                                                | 12     |

| <ul> <li>4.3 Data transaction controller (DTC)</li></ul>                                                                                                                                                                                                                                                                                                                            | 12     |

| <ul><li>5 Clock system</li><li>6 Debugging system</li></ul>                                                                                                                                                                                                                                                                                                                         | 15     |

| 6 Debugging system                                                                                                                                                                                                                                                                                                                                                                  | 17     |

|                                                                                                                                                                                                                                                                                                                                                                                     | 18     |

| 7 Peripheral devices                                                                                                                                                                                                                                                                                                                                                                | 19     |

|                                                                                                                                                                                                                                                                                                                                                                                     | 20     |

| 7.1 Input-output port (GPIO)                                                                                                                                                                                                                                                                                                                                                        | 20     |

| 7.1.1 Brief characteristics                                                                                                                                                                                                                                                                                                                                                         |        |

| 7.1.2 GPIO functioning                                                                                                                                                                                                                                                                                                                                                              | 20     |

| 7.1.3 Register description                                                                                                                                                                                                                                                                                                                                                          |        |

| 7.2 External memory bus controller (MCTRL0)                                                                                                                                                                                                                                                                                                                                         |        |

| 7.2.1 Short description                                                                                                                                                                                                                                                                                                                                                             | 24     |

| 7.2.2 Интерфейс PROM, I/O                                                                                                                                                                                                                                                                                                                                                           | 25     |

| 7.2.3 Интерфейс SDRAM                                                                                                                                                                                                                                                                                                                                                               |        |

| 7.3 $UART(UARTx)$ interface                                                                                                                                                                                                                                                                                                                                                         | 28     |

| 7.3.1 Brief characteristics                                                                                                                                                                                                                                                                                                                                                         | 28     |

| 7.3.2 Data transmission                                                                                                                                                                                                                                                                                                                                                             | 28     |

| 7.3.3 Data receipt $\ldots$                                                                                                                                                                                                                                                                        | 29     |

| 7.3.4 Transmission speed settings                                                                                                                                                                                                                                                                                                                                                   |        |

| 7.3.5 Self-test modes                                                                                                                                                                                                                                                                                                                                                               |        |

| 7.3.5.1 Self-test mode on interface line level                                                                                                                                                                                                                                                                                                                                      |        |

13.03.2014

|     |         | 7.3.5.2 Self-test mode on data level                                                                                             |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------|

|     | 7.3.6   | Interrupt formation                                                                                                              |

|     |         | 7.3.6.1 Receiver pending interrupt mode                                                                                          |

|     | 7.3.7   | Registers' description                                                                                                           |

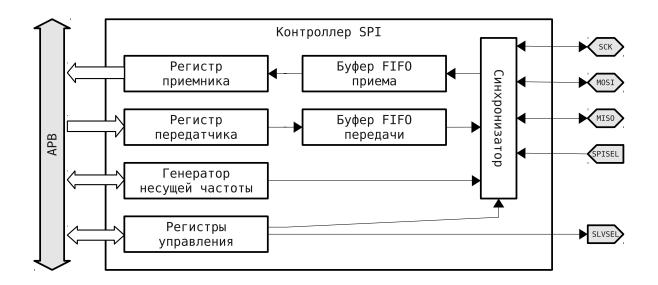

| 7.4 | SPI in  | terface (SPIx)                                                                                                                   |

|     | 7.4.1   | General characteristics                                                                                                          |

|     | 7.4.2   | 3-wire operation $\ldots \ldots 37$                               |

|     | 7.4.3   | Data receive and transmit                                                                                                        |

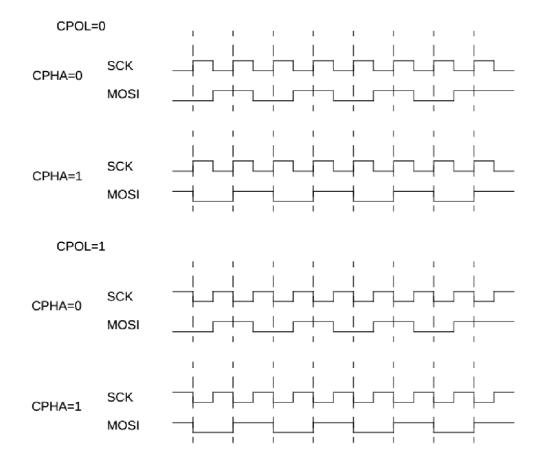

|     | 7.4.4   | SCK clock signal                                                                                                                 |

|     | 7.4.5   | Operation in «master» mode                                                                                                       |

|     | 7.4.6   | Operation in «slave» mode                                                                                                        |

|     | 7.4.7   | Description of registers                                                                                                         |

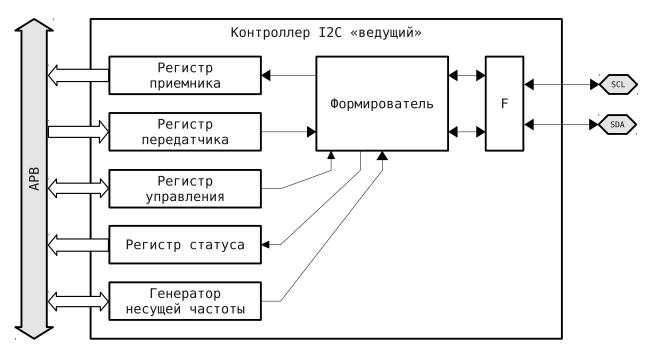

| 7.5 | Interfa | ace $I^2C$ «master» (I2C0)                                                                                                       |

|     | 7.5.1   | Brief characteristics                                                                                                            |

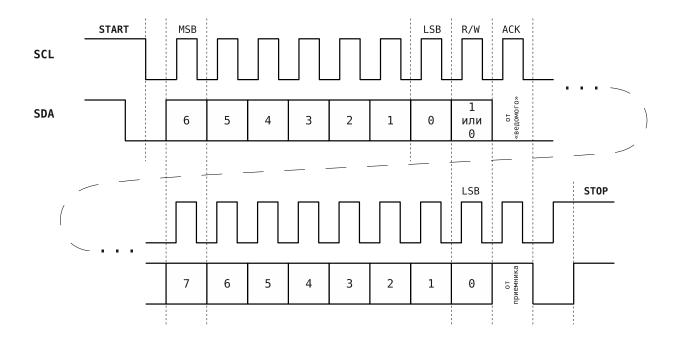

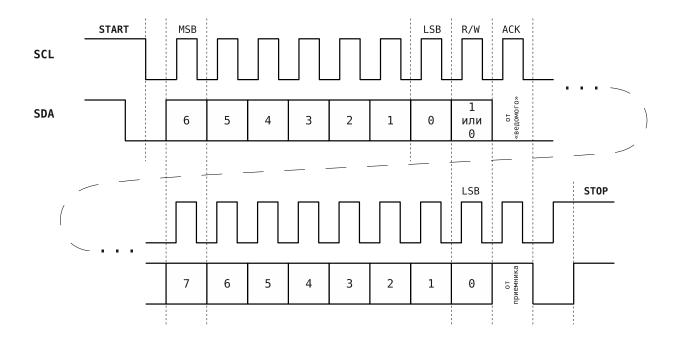

|     | 7.5.2   | General description of receive-transmit protocol                                                                                 |

|     | 7.5.3   | Carrier frequency generation                                                                                                     |

|     | 7.5.4   | Interface operation algorythm                                                                                                    |

|     |         | 7.5.4.1 Data record $\ldots \ldots 44$                     |

|     |         | 7.5.4.2 Data reading                                                                                                             |

|     | 7.5.5   | Description of registers                                                                                                         |

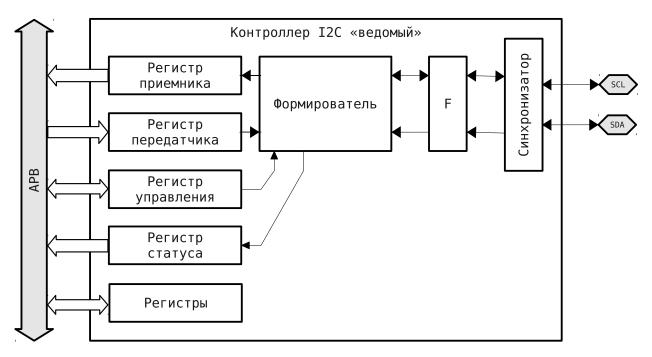

| 7.6 | Interfa | ace $I^2C$ «slave» (I2C1)                                                                                                        |

|     | 7.6.1   | Brief characteristics                                                                                                            |

|     | 7.6.2   | General description of receive-transmit protocol                                                                                 |

|     | 7.6.3   | Carrier frequency generation                                                                                                     |

|     | 7.6.4   | Interface operation algorythm                                                                                                    |

|     |         | 7.6.4.1 Data receipt from «master»                                                                                               |

|     |         | 7.6.4.2 Data transmission to «master»                                                                                            |

|     | 7.6.5   | description of registers                                                                                                         |

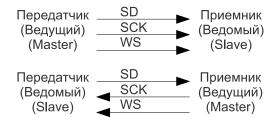

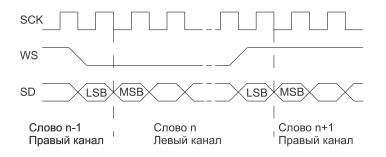

| 7.7 | Contr   | oller $I^2S(I2Sx)$                                                                                                               |

|     | 7.7.1   | Brief characteristics                                                                                                            |

|     | 7.7.2   | Bus general description $I^2S$                                                                                                   |

|     | 7.7.3   | Description of registers                                                                                                         |

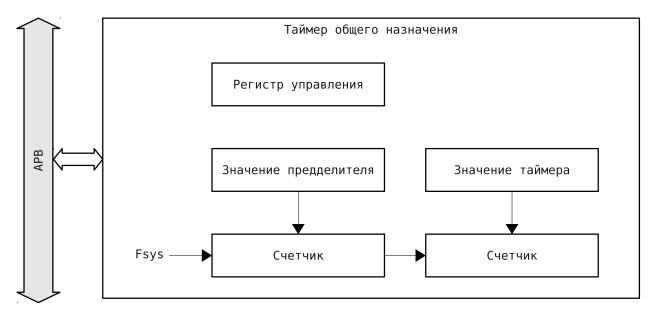

| 7.8 | genera  | al purpose timer (GPTIMx) $\ldots \ldots 61$               |

|     | 7.8.1   | Brief characteristics                                                                                                            |

|     | 7.8.2   | Work alogorythm                                                                                                                  |

|     | 7.8.3   | Register description                                                                                                             |

| 7.9 | Contr   | oller Ethernet(Ethernet0) $\ldots \ldots 65$ |

13.03.2014

### USER MANUAL

|      | 7.9.1    | Brief description                                                                                                                                                 |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 7.9.2    | Clocking                                                                                                                                                          |

|      | 7.9.3    | Access to internal FIFO receive-transmit buffers                                                                                                                  |

|      | 7.9.4    | Transmitter DMAC                                                                                                                                                  |

|      |          | 7.9.4.1 Decriptor setting $\ldots \ldots \ldots$  |

|      |          | 7.9.4.2 Data preparation for transmission                                                                                                                         |

|      |          | 7.9.4.3 Data transmission                                                                                                                                         |

|      |          | 7.9.4.4 Descriptor operation after data transmission completion $\dots 67$                                                                                        |

|      | 7.9.5    | Receiver DMAC                                                                                                                                                     |

|      |          | 7.9.5.1 Descriptor setting $\ldots \ldots \ldots$ |

|      |          | 7.9.5.2 Data receipt                                                                                                                                              |

|      |          | 7.9.5.3 Descriptor processing after date transmission is finished 69                                                                                              |

|      | 7.9.6    | Description of registers                                                                                                                                          |

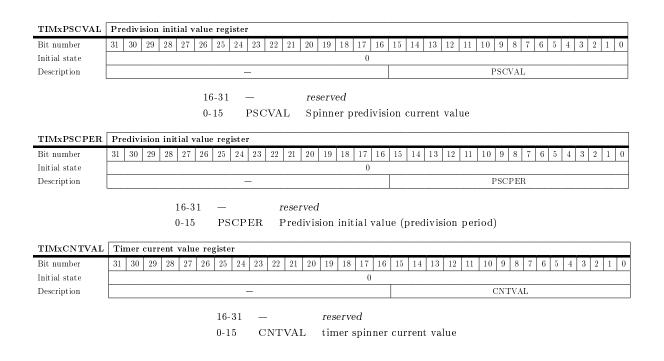

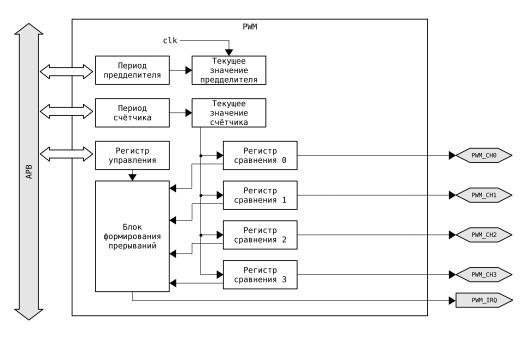

| 7.10 | PWM      | $controller (PWMx)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                              |

|      | 7.10.1   | Brief characteristics                                                                                                                                             |

|      | 7.10.2   | PWM initialization                                                                                                                                                |

|      | 7.10.3   | PWM operation modes                                                                                                                                               |

|      | 7.10.4   | PWM Interrupts                                                                                                                                                    |

|      | 7.10.5   | PWM pulse duration                                                                                                                                                |

|      | 7.10.6   | Description of registors                                                                                                                                          |

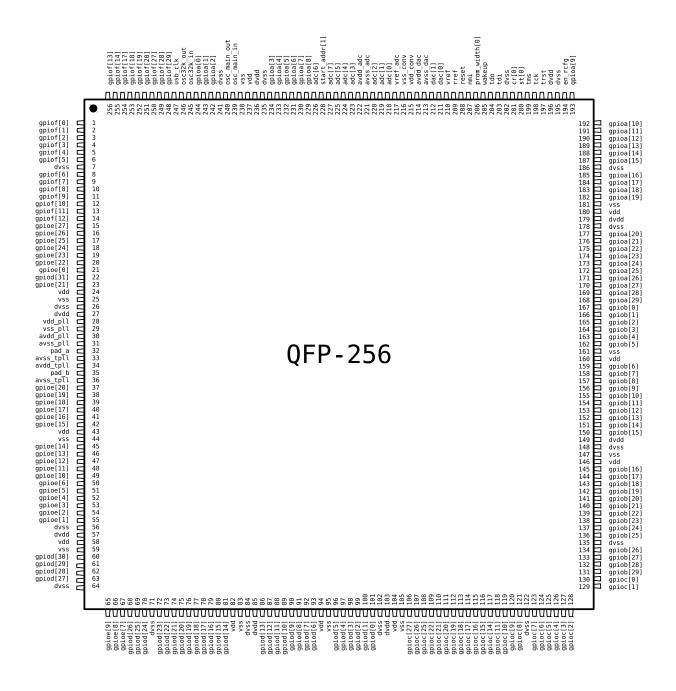

| Pro  | cessor?  | 's pinmap assignation 78                                                                                                                                          |

| 8.1  | Proces   | $ssor input/output table QFP 256 \dots 78$                                                                                                                        |

| 8.2  | Proces   | ssor output diagram in QFP256 package                                                                                                                             |

| Ele  | ctric cł | haracteristics 85                                                                                                                                                 |

| 9.1  | Electri  | ical characteristics of input-output ports                                                                                                                        |

8

9

# 1 Type codes and abbreviations

## 1.1 List of abbreviations

- MP microprocessor;

- SW software;

- MSb most significant bit;

- MSB most significant bit;

- LSb least significant bit;

- LSB least significant bit;

- RAM random access memory;

- PM program memory;

- DM data memory;

- DMA direct memory access;

- GPR— general purpose register(s);

### 1.2 conventional Type Codes

- '1', '0'— state of logical item, logical zero, accordingly;

- REG(BIT) this record is used for pointing bit in register, where REG is register's name, and BIT is an indication of bit group in it. For example, "bit I2CxCR(EN)" signifies that there is a designation at EN bit of I2CxCR register, and "I2CxPSC(PSC)" signifies bit group PSC. To find out more details about designated registers and bits, see these registers' description

- PUx, BLOCKx, PUxREG In the notations of registers, PU and MP names sumbol "x" can be used. This is digit replacement, for example, there are several identical peritheral UART blocks possessing digits 0,1 and so on. For UART0 "x" it is 0. If there is I2CxCR register then register for I2C0 is being called I2C0CR

# 2 Description

## 2.1 General technical characteristics

| Notation                    | MCp042P200102/MCp042R100102               |

|-----------------------------|-------------------------------------------|

| General purpose of function | 64-bit processor                          |

| Multicellular core          | 4 cells 32/64bit                          |

| FPU(ieee754)                | single/double precision                   |

| Peak performance            | 24 MFLOPS/MГц                             |

| Internal SRAM, KiB          | 512                                       |

| External memory bus, bit    | 32                                        |

| USB 2.0 FS device           | 1                                         |

| UART                        | 4                                         |

| SPI                         | 2                                         |

| I2C                         | 1 "master", 1 "slave"                     |

| I2S                         | 1 "master"/"slave" (receiver/transceiver) |

| PWM                         | 1, 4 channels                             |

| Ethernet 10/100             | 1                                         |

| DAC, 12bit, 125ksps,        | 2 channels                                |

| ADC, 16bit, 48ksps,         | 8 channels                                |

| GPIO pins                   | 166                                       |

6 - 85

### 2.2 MP structure

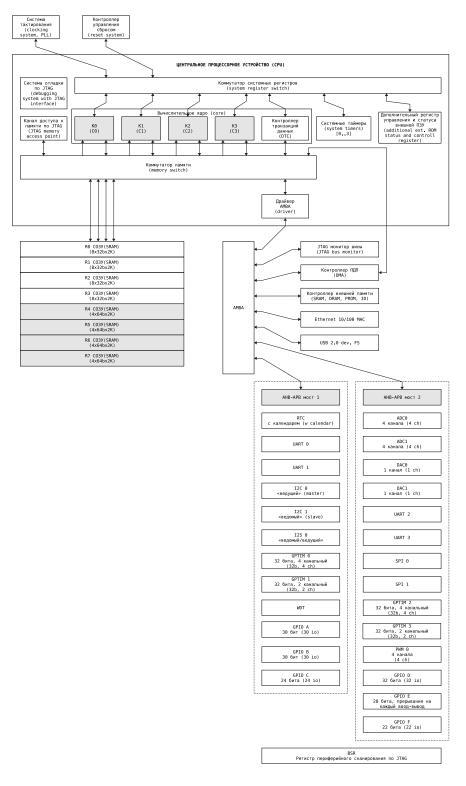

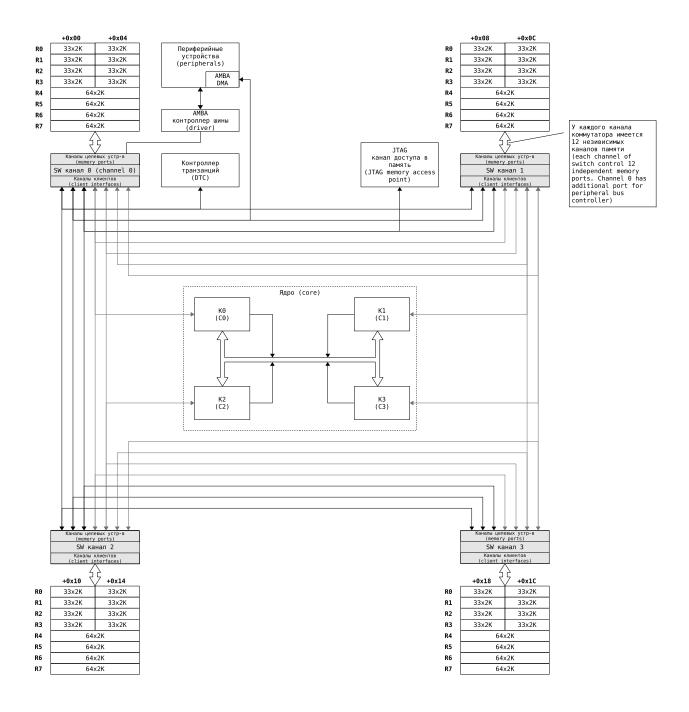

Figure 1: General structure of MCp042P200102/MCp042R100102

www.multiclet.com

### MP consist of:

- CPU;

- Peripheral devices. Peripheral bus is AMBA 2.0;

- SRAM.

# 3 Central processor unit

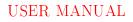

Figure 2: CPU block scheme

CPU consist of:

- 4 cellular processing unit;

- memory switch;

- system peripherals;

- system peripherals switch;

- debugging system.

Block scheme of CPU present on pic. 2.

### 3.1 Registers

All registers exept system are 64bit width. General purpose (GPR), index and control registers have copies in each cell. It's necessary for MCp042R100102, because when we reconfigure CPU we need to see registers in each group of cells. System peripherals registers are situated in system peripherals like PLL, System timers etc. There are shared resouces.

| #          | Register           | Description                                                  |

|------------|--------------------|--------------------------------------------------------------|

|            | GPR, index regis   | ters (copies in each cell)                                   |

| 0-7        | нет                | GPR                                                          |

| 8-15       | нет                | index registers                                              |

|            | System per         | ripherals registers                                          |

| 16         | PLLCR              | control register of PLL                                      |

| 17         | PLLSTR             | status register of PLL                                       |

| 18         | PLLTMCR            | controll register of test block of PLL                       |

| 19         | MCTRL_CH0_CPR      | switch ch 0 control                                          |

| 20         | MCTRL CH1 CPR      | switch ch 1 control                                          |

| 21         | MCTRL_CH2_CPR      | switch ch 2 control                                          |

| 22         | MCTRL CH3 CPR      | switch ch 3 control                                          |

| 23         | STOPRDR            | system timer 0 period                                        |

| 24         | ST1PRDR            | system timer 1 period                                        |

| 25         | ST2PRDR            | system timer 2 period                                        |

| 26         | ST3PRDR            | system timer 3 period                                        |

| 27         | ST0CR              | system timer 0 control                                       |

| 28         | ST1CR              | system timer 1 control                                       |

| 29         | ST2CR              | system timer 2 control                                       |

| 30         | ST3CR              | system timer 3 control                                       |

| 31         | reserved           |                                                              |

| 32         | STOVAL             | curent value of system timer 0                               |

| 33         | ST1VAL             | curent value of system timer 1                               |

| 34         | ST2VAL             | curent value of system timer 2                               |

| 35         | ST3VAL             | curent value of system timer 3                               |

| 36-39      | reserved           |                                                              |

| 40         | DTC CTRL           | DTC control register                                         |

| 41         | DTC ST             | DTC status register                                          |

| 42         | DTC IMASK0         | DTC mask 0 register                                          |

| 43         | DTC IMASK1         | DTC mask 1 register                                          |

| 44         | DTC DATA           | DTC data register                                            |

| 45         | DTC S ADDR         | DTC source address                                           |

| 46         | DTC D ADDR         | DTC destination address                                      |

| 47         | ROM CTRL           | external PROM status and control                             |

|            | _                  | rs (copies in each cell)                                     |

| 48         | PSW                | processor state register                                     |

| 49         | INTR               | interrupts                                                   |

| -19<br>50  | MSKR               | interrupts mask                                              |

| 50<br>51   | ER                 | errors and exceptions                                        |

| 52         | IRETADDR           | return address                                               |

| 53         | FORCE              | force interrupts                                             |

| 54         | reserved           | Teres montapos                                               |

| 55         | IHOOKADDR          | interrupt handler address                                    |

| $55 \\ 56$ | INTNUM             | current pending interrupt number                             |

| 50<br>57   | REGMOD             | index registers modification                                 |

| 57<br>58   | LASTADDR           | address of previous paragraph                                |

|            |                    | address of previous paragraph<br>address of curent paragraph |

| 59         | CURRENTADDR        |                                                              |

|            | NEWADDR<br>LASTDSW | address of next paragraph<br>last value of PSW               |

| 61         | LASTPSW            |                                                              |

| 62         | reserved           |                                                              |

| 63         | ICR                | reconfiguration control                                      |

Table 2: MP registers

# 4 Memory organization

Program model of memory of MCp042P200102 / MCp042R100102 looks like solid massive of bytes. Address range:  $[0, 2^{32}]$ . Memory space is common for code and data, but there is some restriction for their placement.

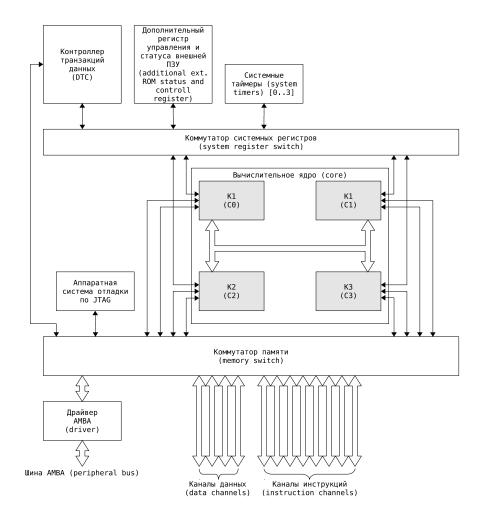

### 4.1 Memory map

We can see some regions of the memory (pic.??):

- on chip memory;

- external RAM;

- external ROM;

- I/O space;

- image of 0x0000000-0x40000000 address range;

- peripheral bus.

### **On chip memory.** This is SRAM.

There are 4 regions in 0x0000000-0x00040000 address range. There are 32 physical blocks  $33 \times 2^{11}$ , that provide access to neighbor addresses at the same time. Bit 33 used by debugging system only (ch.??). These regions are specialized for code. You can place here code and data. Only these regions provide unlimited number hardware brakepoints for programs.

Block number you can calculate with a next expression:

$$n = \left\lceil \frac{A_b}{2^{16}} \right\rceil + \left\lceil \frac{A_b \mod 32}{8} \right\rceil, \ A_b = [0, 2^{18} - 1]$$

Address in bytes, result is a minimal integer number after division.

There are 4 regions in 0x00040000-0x00080000 address range. There are 16 physical blocks  $64 \times 2^{11}$ , that provide access to neighbor addresses at the same time. Don't use these regions for code that you whant to execute. Because it's possible that cells will request information from the same physical block at the same time and it will cause of delay. But you can store code here.

Figure 3: Memory map

Block number you can calculate with a next expression:

$$n = \left\lceil \frac{A_b}{2^{16}} \right\rceil + \left\lceil \frac{A_b \mod 32}{4} \right\rceil, \ A_b = [2^{18}, 2^{19} - 1]$$

Address in bytes, result is a minimal integer number after division.

**External RAM, external ROM, I/O space** There is special interface that provide access to these regions of memory. (see ch.7). You can srore data and code, execute programm in these regions. But it's slower than you will use on-chip memory.

**Image of 0x0000000-0x40000000 address range.** This region used by peripheral DMA controller for access to first 1GiB address space. (ch.7).

Peripheral bus. Peripheral bus addresses.

## 4.2 Memory switch

Figure 4: Switch structure

Switch has 4 independent channels, that controll dedicated memory blocks. Each channel has 15 clients access channels and 12 independent memory ports. Channel «0» has additional peripheral bus channel.

Switch channel number ypu can calculate with next expression:

$$n = \left\lceil \frac{A_b \mod 32}{4} \right\rceil$$

Address in bytes, result is a minimal integer number after division.

Client sends request to all switch channel at the same time. If channel can service this request then it will reply with data after some time. If clients requested the same address then they will be served according priority.

| #  | Client ports   | Description              |

|----|----------------|--------------------------|

| 0  | $C0_I_0$       | Instruction channels     |

| 1  | C0_I_1         | 32bit data width         |

| 2  | C1_I_0         |                          |

| 3  | C1_I_1         |                          |

| 4  | C2_I_0         |                          |

| 5  | C2_I_1         |                          |

| 6  | $C3_I_0$       |                          |

| 7  | C3_I_1         |                          |

| 8  | C0_D           | Data channels            |

| 9  | C1_D           |                          |

| 10 | C2_D           |                          |

| 11 | C3_D           |                          |

| 12 | DTC_INDEX      | DTC channel              |

| 13 | AMBA_DMA_INDEX | peripheral DMA channel   |

| 14 | JTAG_MEM_INDEX | Debugging system channel |

Table 3: Clients of switch channel

| #  | Memory ports | Description                   |

|----|--------------|-------------------------------|

| 0  | $R0_0$       | Region 0-3 of memory          |

| 1  | $R0_1$       | 32bit data width              |

| 2  | R1_0         |                               |

| 3  | R1_1         |                               |

| 4  | R2_0         |                               |

| 5  | R2_1         |                               |

| 6  | R3_0         |                               |

| 7  | R3_1         |                               |

| 8  | R4           | Region 4-7 of memory          |

| 9  | R5           | 64bit data width              |

| 10 | R6           |                               |

| 11 | R7           |                               |

| 12 | AMBA         | Address space after R7 region |

Table 4: Memory ports of switch channel

Switch channel has priority scheme. Client channels devided by 4 types:

- instruction channel;

- data channel;

- AMBA(peripheral) channel;

- DTC channel.

# 4.3 Data transaction controller (DTC)

# 5 Clock system

# 6 Debugging system

# 7 Peripheral devices

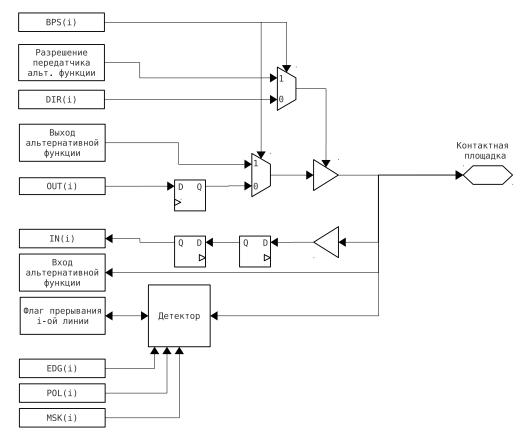

# 7.1 Input-output port (GPIO)

### 7.1.1 Brief characteristics

- MP contains 2 32-bit ports, 1 24-bit ports and 1 16-bit;

- Each port bit can be individually configured at inputs or outputs and can optionally generate interrupts;

- interrupt request can be formed in accordance with signal level or edge (front/back);

- port inputs-outputs can be switched to alternative function;

Figure 5: Block diagramm of i line GPIO

### 7.1.2 GPIO functioning

Input-output ports are implemented as bi-directional buffers with programmable output definition. Each buffer's input is synchronized by means of two series-connected flip-flops

to prevent the possibility of metastability. The synchronized value may be read from data receiving register (GPIOxIN) of input-output port. The output definition is controlled by transmission permit register (GPIOxDIR). Logical unit ('1') in the given bit of input-output port configures its corresponding line to the output. The output value is taken from the register of the transmitted data (GPIOxOUT) of input-output port.

Each input-output port line can be configured to form an interrupt. Formation of interrupt is controlled by three registers: interrupt mask register (GPIOxMSK), register of interrupt event settings, signal polarity register (GPIOxPOL), and signal component register (GPI-OxEDG). To enable the interrupt corresponding interrupt mask bit has to be set (one). If signal component register is reset (zero), an interrupt is generated by signal level. If signal polarity register is reset (zero), an interrupt occurs in case of active low level signal, if signal component register is set (one), an interrupt is generated by signal edge. If signal polarity register is reset (zero), an interrupt is case of front signal edge. If signal polarity register is reset (zero), an interrupt occurs in case of front signal edge. If signal polarity register is set (one), an interrupt occurs in case of front signal edge.

Each input-output port can be shared for other signal types that perform alternate functions. To enable the task of some port line's alternate functions task corresponding bit (one) is to be set in alternative functions permit register (GPIOxBPS) A description of all inputs-outputs in MP find in Section ??

### 7.1.3 Register description

General purpose input-output ports:

| GPIOA: basic address - 0xC01F 0000; port width - 32 bits. |

|-----------------------------------------------------------|

| GPIOB: basic address - 0xC01F 0100; port width - 32 bits. |

| GPIOC: basic address - 0xC01F 0200; port width - 24 bits. |

| GPIOD: basic address - 0xC01F 0300; port width - 16 bits. |

To get the real address of the register the register address's offset should be added to base (initial) address on the bus.

Bits from 0 to 31 are significant for ports A, B, bits from 0 to 23 are significant for port C, bits from 0 to 15 are significant for port D. Reading the bits from 24 to 31 for port C and from 16 to 31 for the port D will give a zero result and the record will be ineffectual.

| Регистр  | Address displacement | Access | Description                                         |

|----------|----------------------|--------|-----------------------------------------------------|

| GPIOxIN  | $00\mathrm{h}$       | R      | Receiving data register.                            |

| GPIOxOUT | 04h                  | RW     | Transmitted data register.                          |

| GPIOxDIR | 08 h                 | RW     | Transmission enabling register.                     |

| GPIOxMSK | 0Ch                  | RW     | Mask interrupt register.                            |

| GPIOxPOL | 10 h                 | RW     | Event interrupt setting register, signal polarity.  |

| GPIOxEDG | 14h                  | RW     | Event interrupt setting register, signal component. |

| GPIOxBPS | 18h                  | RW     | Alternative functions enabling register             |

| GPIOxIN | Receiving | data | register |  |

|---------|-----------|------|----------|--|

| di ioxin      | 100 | CCIVI | ung ( | iata | regi | ater |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|---------------|-----|-------|-------|------|------|------|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit number    | 31  | 30    | 29    | 28   | 27   | 26   | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17  | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Initial state | 0   | 0     | 0     | 0    | 0    | 0    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Description   |     |       |       |      |      |      |    |    |    |    |    |    |    |    | DAT | ΓA |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

0-31 DATA Receiving data register. Each regiter bit corresponds with each port line.

| GPIOxOUT      | Re | ceivi | ing c | lata | regi | ster |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|---------------|----|-------|-------|------|------|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit number    | 31 | 30    | 29    | 28   | 27   | 26   | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Initial state | 0  | 0     | 0     | 0    | 0    | 0    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Description   |    | DATA  |       |      |      |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|               |    |       |       |      |      |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | _ |

0-31 DATA Receiving data register. Each register bit corresponds with each port line.

| GPIOxDIR      | Tra | nsm | issic | on ei | ıabl | ing 1 | egis | ter |    |    |    |    |    |    |     |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|---------------|-----|-----|-------|-------|------|-------|------|-----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit number    | 31  | 30  | 29    | 28    | 27   | 26    | 25   | 24  | 23 | 22 | 21 | 20 | 19 | 18 | 17  | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Initial state | 0   | 0   | 0     | 0     | 0    | 0     | 0    | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Description   |     |     |       |       |      |       |      |     |    |    |    |    |    |    | DAT | Ά  |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

0-31 DATA Transmission enabling register. Each register bit corresponds with each port line. If any register bit is set in '1', then in relevant port line data trasmission is allowed, if bit is set in '0'-transmission is forbidden.

| GPIOxMSK      | Int                                                                                                                                                                                                                                                                                                                                                                                             | erru | ipt                  | masl   | s reg | ziste | r     |       |       |      |       |       |     |                        | _     |       |               |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|--------|-------|-------|-------|-------|-------|------|-------|-------|-----|------------------------|-------|-------|---------------|------------------------------|------|-------------|------|---------------|------|------|------|------|------|-----|-------|------|------|------|----|

| Bit number    | 31                                                                                                                                                                                                                                                                                                                                                                                              | 30   | -                    | 9 28   | _     | 26    | 25    | 24    | 23    | 22   | 2 21  | 20    | 1   | 9 18                   | 17    | 16    | 15            | 14                           | 13   | 3 1         | 2 1  | 1 :           | 10   | 9    | 8    | 7    | 6    | 5   | 4     | 3    | 2    | 1    | 0  |

| Initial state | 0                                                                                                                                                                                                                                                                                                                                                                                               | 0    |                      | 0 0    | 0     | 0     | 0     | 0     | 0     | 0    | 0     | 0     | 1   | 0 0                    | 0     | 0     | 0             | 0                            | 0    | +           | 0 (  | 0             | 0    | 0    | 0    | 0    | 0    | 0   | 0     | 0    | 0    | 0    | 0  |

| Description   |                                                                                                                                                                                                                                                                                                                                                                                                 |      | _                    |        | _     | _     | 1     |       | -     | _    | _     | 1     | -   |                        | DA    | ГА    |               |                              | -    |             | _    |               |      |      |      |      |      |     |       |      |      |      |    |

|               | L                                                                                                                                                                                                                                                                                                                                                                                               |      |                      |        |       |       |       |       |       |      |       |       |     |                        |       |       |               |                              |      |             |      |               |      |      |      |      |      |     |       |      | _    |      |    |

| 0 - 31        | DA                                                                                                                                                                                                                                                                                                                                                                                              | ТA   |                      | Inte   | erru  | pt r  | nasl  | k re  | gist  | er.  | Eac   | ch re | egi | $\operatorname{ister}$ | bit   | corr  | esp           | ond                          | ls w | itl         | n ea | $^{\rm ch}$   | poi  | rt l | line | e    | lf a | any | / r   | egis | ste  | r b  | it |

|               |                                                                                                                                                                                                                                                                                                                                                                                                 |      |                      | is s   | et ir | 1 '1  | , th  | ien i | in re | elev | vant  | por   | t   | line o                 | lata  | eve   | $\mathbf{nt}$ | $\operatorname{int}\epsilon$ | erru | $_{\rm pt}$ | is a | llov          | vec  | l, i | f b  | it i | s s  | set | in    | ·0 · | - e  | ever | nt |

|               |                                                                                                                                                                                                                                                                                                                                                                                                 |      |                      | inte   | rruj  | pt is | s foi | bid   | den.  |      |       |       |     |                        |       |       |               |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

|               | Event interrupt setting register, signal polarity                                                                                                                                                                                                                                                                                                                                               |      |                      |        |       |       |       |       |       |      |       |       |     |                        |       |       |               |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

| GPIOxPOL      | Event interrupt setting register, signal polarity           31         30         29         28         27         26         25         24         23         22         21         20         19         18         17         16         15         14         13         12         11         10         9         8         7         6         5         4         3         2         1 |      |                      |        |       |       |       |       |       |      |       |       |     |                        |       |       |               |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

| Bit number    | 31                                                                                                                                                                                                                                                                                                                                                                                              | 30   | 29                   | 9 28   | 27    | 26    | 25    | 24    | 23    | 22   | 21    | 20    | 19  | 9 18                   | 17    | 16    | 15            | 14                           | 13   | 1           | 2 11 | l 1           | 0    | 9    | 8    | 7    | 6    | 5   | 4     | 3    | 2    | 1    | 0  |

| Initial state | 0                                                                                                                                                                                                                                                                                                                                                                                               | 0    | 0                    | ) ()   | 0     | 0     | 0     | 0     | 0     | 0    | 0     | 0     | 0   | ) 0                    | 0     | 0     | 0             | 0                            | 0    | (           | ) 0  | (             | )    | 0    | 0    | 0    | 0    | 0   | 0     | 0    | 0    | 0    | 0  |

| Description   | DATA                                                                                                                                                                                                                                                                                                                                                                                            |      |                      |        |       |       |       |       |       |      |       |       |     |                        |       |       |               |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

|               |                                                                                                                                                                                                                                                                                                                                                                                                 |      |                      |        |       |       |       |       |       |      |       |       |     |                        |       |       |               |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

| 0 - 31        | DATA Event interrupt setting register, signal polarity. Each register bit corresponds with each polarity.                                                                                                                                                                                                                                                                                       |      |                      |        |       |       |       |       |       |      |       |       |     |                        |       | -     |               |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

|               | line. If any register bit is set in '1', then relevant port line forms interruption under leadi                                                                                                                                                                                                                                                                                                 |      |                      |        |       |       |       |       |       |      |       |       |     |                        |       |       | 0             |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

|               | line. If any register bit is set in '1', then relevant port line forms interruption under leading edge/high level, if bit is set in '0'- forms interrution under trailing edge/low level. Edge or le                                                                                                                                                                                            |      |                      |        |       |       |       |       |       |      |       |       |     |                        |       | lev   | el            |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

|               |                                                                                                                                                                                                                                                                                                                                                                                                 |      |                      | cho    | ice o | dep   | ends  | s on  | set   | tin  | gs of | f rel | ev  | ant t                  | oit i | ı reg | gist          | er (                         | GΡΙ  | O           | κED  | $\mathbf{G}.$ |      |      |      |      |      |     |       |      |      |      |    |

|               |                                                                                                                                                                                                                                                                                                                                                                                                 |      |                      |        |       |       |       |       |       |      |       |       |     |                        |       |       |               |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

| GPIOxEDG      | Ev                                                                                                                                                                                                                                                                                                                                                                                              | ent  | $\operatorname{int}$ | errup  | t set | tting | reg   | ister | , sig | nal  | com   | pone  | ent | ;                      |       |       |               | _                            |      |             |      |               |      |      |      |      |      |     | _     |      | _    |      |    |

| Bit number    | 31                                                                                                                                                                                                                                                                                                                                                                                              | 30   | 2                    | 9 28   | 27    | 26    | 25    | 24    | 23    | 22   | 21    | 20    | 1   | 9 18                   | 17    | 16    | 15            | 14                           | 13   | 1           | 2 1  | 1 1           | _    | -    | 8    | -    |      | 5   | 4     | 3    | 2    | 1    | 0  |

| Initial state | 0                                                                                                                                                                                                                                                                                                                                                                                               | 0    | (                    | 0 0    | 0     | 0     | 0     | 0     | 0     | 0    | 0     | 0     | (   | 0 0                    | 0     | 0     | 0             | 0                            | 0    |             | 0 0  | )             | 0    | 0    | 0    | 0    | 0    | 0   | 0     | 0    | 0    | 0    | 0  |

| Description   |                                                                                                                                                                                                                                                                                                                                                                                                 |      |                      |        |       |       |       |       |       |      |       |       |     |                        | DA    | ГА    |               |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

| 0.91          | <b>D</b> 4                                                                                                                                                                                                                                                                                                                                                                                      |      |                      | Б      | , .   |       |       |       |       |      | • ,   |       |     | 1                      |       |       |               | Б                            | 1    |             |      | · ·           |      |      |      |      | 1    |     | • • • |      | 1    |      |    |

| 0-31          | DA                                                                                                                                                                                                                                                                                                                                                                                              | ΠA   |                      |        |       |       | -     |       |       | 0    | 0     |       | 0   | gnal c                 |       |       |               |                              |      | 0           | ·    |               |      |      | -    |      |      |     |       |      |      | -    |    |

|               |                                                                                                                                                                                                                                                                                                                                                                                                 |      |                      |        |       |       | -     |       |       |      |       |       |     | , the                  |       |       | nt p          | oort                         | lın  | еt          | orm  | s ir          | itei | rru  | ptı  | on   | ur   | ıde | r e   | dge  | а, 1 | it b | ıt |

|               |                                                                                                                                                                                                                                                                                                                                                                                                 |      |                      | is s   | et ir | ı '0' | - it  | forr  | ns i  | nte  | errup | otior | nι  | ındeı                  | lev   | el.   |               |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

|               | 4.1.                                                                                                                                                                                                                                                                                                                                                                                            |      |                      |        |       |       |       |       |       |      |       |       |     |                        |       |       |               |                              |      |             |      |               |      |      |      |      |      |     |       |      |      |      | _  |

| GPIOxBPS      | _                                                                                                                                                                                                                                                                                                                                                                                               |      |                      | ze fun | _     | _     | _     |       | -     |      |       |       |     |                        |       |       |               |                              |      |             |      | _             |      | -    | -    | -    | _    |     |       |      |      | .    | _  |

| Bit number    | 31                                                                                                                                                                                                                                                                                                                                                                                              | 30   | 29                   | _      | 27    | 26    | 25    | 24    | 23    | 22   | 21    | 20    | 19  |                        | 17    |       | 15            | 14                           | 13   | 1:          | _    | _             | _    | _    |      | _    | -    | -   | 4     |      | 2    | _    | 0  |

| Initial state | 0                                                                                                                                                                                                                                                                                                                                                                                               | 0    | 0                    | 0      | 0     | 0     | 0     | 0     | 0     | 0    | 0     | 0     | 0   | 0                      | 0     | 0     | 0             | 0                            | 0    | 0           | 0 0  | 0             | 1    | 0    | 0    | 0    | 0    | 0   | 0     | 0    | 0    | 0    | 0  |

| Description   |                                                                                                                                                                                                                                                                                                                                                                                                 |      |                      |        | -     |       |       |       |       |      |       |       |     |                        | DAT   | Ά     |               | -                            |      |             |      |               |      |      |      |      |      |     |       |      |      |      |    |

0-31 DATA Alternative functions enabling register. Each register bit corresponds with each port line. If any register bit is set in '1', then relevant port line is allowed to imlement alternative function, if bit is set in '0'- imlementation of alternative function is forbidden.

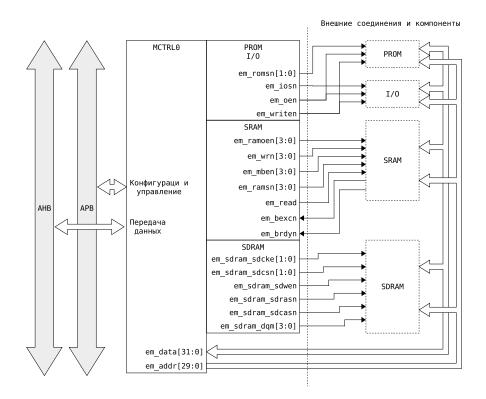

## 7.2 External memory bus controller (MCTRL0)

#### 7.2.1 Short description

- поддерживает работу с памятью типа: PROM, DRAM, SRAM;

- автоматическое регенерация SDRAM;

- внешняя шина данных до 32 бит;

- работа с устройствами ввода/вывода (I/O);

Figure 6: Контроллер шины внешней памяти

Контроллер может управлять 2-мя банками PROM, одним банком I/O, пятью банками SRAM и двумя банками SDRAM.

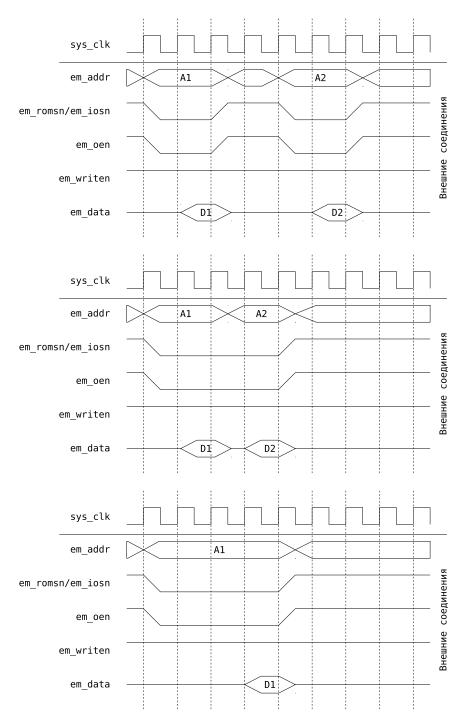

### 7.2.2 Интерфейс PROM, I/O

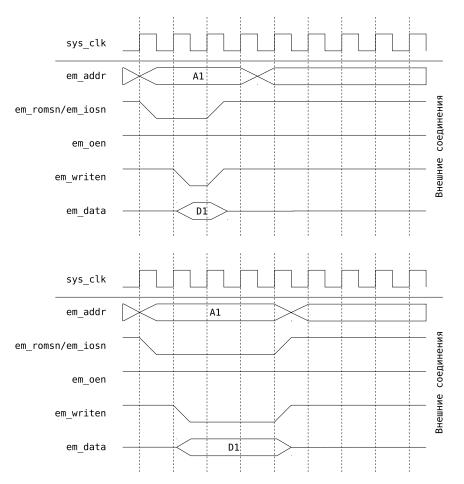

Ниже приведены диаграммы работы интерфейса.

Диаграммы чтения:

Figure 7: Диаграммы чтения PORM, I/O (независимые чтения, непрерывное чтение и чтение с 2-мя циклами ожидания)

### Диграммы записи:

Figure 8: Диаграммы записи PORM, I/O (без циклов ожидания и с 2-мя циклами ожидания)

### 7.2.3 Интерфейс SDRAM

Ниже приведены диаграммы работы интерфейса.

## 7.3 UART(UARTx) interface

### 7.3.1 Brief characteristics

- full duplex mode;

- separate FIFO buffers 32 in depth for receive-transmit;

- data word 8 bit, fixed;

- adjustable parity check;

- 1 stop bit;

- built-in data flow check (CTS, RTS);

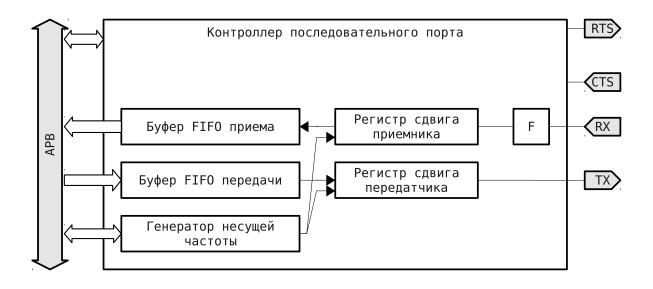

Figure 9: Block diagram UARTx

Fig. 9 is a block diagram of serial UART interface controller.

UART controller automatically generates a parity check bit during transmission and generates parity check when receiving data. Parity check mode turning on/off and setting is implemented in UARTxCR.

### 7.3.2 Data transmission

Transmitter turning and enabling is implemented by UARTxCR(TE). Data for transmission is written in FIFO transmit buffer. Only FIFO input is available for user. Reference to it is

implemented through UARTxDATA. Buffer width - 8 bit, depth - 32.

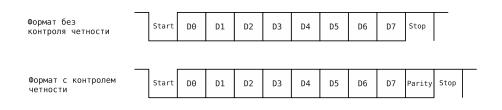

From the FIFO buffer data is sent to the shift register from which they bitwise (LSB) appear at the output TX. Start bit, stop bit and parity check bit (if enabled) are generated automatically. Fig. 10 shows possible transmitted data format, for given controller.

Figure 10: Data burst format

After transmission completion of the last data word from the buffer FIFO, after stop bit formation TX output is set into logic state '1' empty shift register sign is set to UARTxST (TS). After this bit is automatically set to a logic '0 ' once the data appear in FIFO buffer. If the FIFO is empty, bit UARTxST(TE) is set. Bits UARTxST (TF) signalize if buffer is fullthe buffer is full and UARTxST (TH) - less than half of the buffer is full. UARTxST(TCNT) spinner is aimed to control if FIFO buffer is full. UARTxCR(TF) bit controls interrupt requests under buffer events.

When trasmitter operation is forbidden, transmission stops immediately, current data word transmission from shift register is being interrupted as well.

If in-built flow control is enabled, the data from the shift register will be transmitted only if CTS in logic state '0'. If to set signal to logic '1'during the transmission, then the transmission will stop, and is resumed only when CTS is brought back to logic '0'.

### 7.3.3 Data receipt

Bit UARTxCR(RE) switches and enables receiver operation. The received data are being written in FIFO receive buffer. Only FIFO output is available for user in general mode. Addressing it is implemented through UARTxDATA. Buffer width - 8 bit, depth - 32. The received signal passes the digital lowpass filter.

The receiver monitors input signal state and in case of signal transfer from logical state '1 'to state '0' starts receiving data. Through  $\frac{T_{UART}}{2}$  input signal state is fixed, where  $T_{UART}$  - the period of one data word bit. If start bit is not fixed, the receiver will be brought back to sleep mode. If start bit is received, then the remaining data bit words and overhead bits will be received. When last bit is received, data is placed in FIFO buffer, UARTxST(DR) bit is

set. Receipt error bits are set in UARTxST(DR), if such are fixed Error bits are cleansed only by software.

In case when received data are placed in shift register, and FIFO buffer is full, and start bit is fixed at receiver input, shift register data will be lost. Meanwhile UARTxST(OV) bit will be set.

Bits UARTxST(RF) signalize that buffer is full, UARTxST(RH) signalize that less than half of the buffer is full. To control filling of FIFO buffer there is UARTxST(RCNT) spinner. Interrupt request definition under buffer events is controlled by UARTxCR(RF) bit.

If data flow built-in control is enabled and FIFO buffer is full, then RTS transfers into logic state '1'. Once at least one data word is read from the buffer, RTS automatically transfers into logic state '0'.

### 7.3.4 Transmission speed settings

To set data transmission speed there is a system frequency predivision, which division ratio is set in the register UARTxBDR (formula shown below).

$$BRDIV = \frac{F_{sys}}{8 \cdot F_{UART} - 1};$$

#### 7.3.5 Self-test modes

In self-test modes all controller outputs are transfered into inactive mode.

**7.3.5.1** Self-test mode on interface line level In this mode, UART transmitter output commutes with receiver input inside the chip, and CTS signal commutes with RTS. Enabling this mode is implemented by means of UARTxCR(LB) bit setting.

**7.3.5.2** Self-test mode on data level This mode allows recording in FIFO receive buffer and reading from FIFO transmit buffer. Reading and writing are carried out through UARTxFIFODBG register. Enabling this mode is done by setting UARTxCR(LB) bit.

#### 7.3.6 Interrupt formation

Interrupt requests are formed in the following cases:

From transmitter's shift register:

- transmitter operation is enabled: UARTxCR(TE) bit is set;

- transmitter interruptions are enabled: UARTxCR(TI) bit is set.

From FIFO transmit buffer:

- transmitter operation is enabled: UARTxCR(TE) bit is set;

- transmitter interruptions are enabled: UARTxCR(TF) bit is set;

From receiver's shift register:

- transmitter operation is enabled: UARTxCR(RE) bit is set;

- transmitter interruptions are enabled: UARTxCR(RI) bit is set.

From FIFO transmit buffer:

- transmitter operation is enabled: UARTxCR(RE) bit is set;

- transmitter interruptions are enabled: UARTxCR(RF) bit is set;

**7.3.6.1 Receiver pending interrupt mode** The mode is enabled by setting UAR-TxCR(DI) bit. Interrupt from the receiver is formed only in the case of formation of a pause after the last data word receipt. Pause time is equal to 4.5 data word receipt. If the interrupt is enabled from FIFO receive buffer, then an interrupt from shift register will be cleansed. Only buffer interrupts will be active.

Note: The definition of this mode does not affect the formation of the request interruption when receiving transaction completion sign.

### 7.3.7 Registers' description

Base address UART0 - 0xC000 0100 Base address UART1 - 0xC000 0200 Base address UART2 - 0xC010 0100 Base address UART2 - 0xC010 0200

In order to receive real register address add register address diplacement to base (initial) address on the bus.

| Register  | Address displacement | Access | Description                             |

|-----------|----------------------|--------|-----------------------------------------|

| UARTxDATA | 00h                  | RW     | Data register (FIFO)                    |

| UARTxST   | 04h                  | R      | State register                          |

| UARTxCR   | 08h                  | RW     | Control register                        |

| UARTxDBR  | $0\mathrm{ch}$       | RW     | Clock frequency division ratio register |

| UARTxDATA     | Da | ta re | egist | er |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |

|---------------|----|-------|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|

| Bit number    | 31 | 30    | 29    | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| Initial state |    |       |       |    |    |    |    |    | -  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |

| Description   |    | _     |       |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | DA | ТA |   |   |   |   |   |   |   |   |

8-31 — reserved

0-7 DATA Data register. During writing is an input of 32-byte buffer of FIFO transmitter. During reading is an input of 32-byte buffer of FIFO receiver.

| UARTxST       | State regist           | er                       |        |           |        |       |       |       |       |             |        |       |      |   |    |    |    |    |    |    |    |    |    |    |    |

|---------------|------------------------|--------------------------|--------|-----------|--------|-------|-------|-------|-------|-------------|--------|-------|------|---|----|----|----|----|----|----|----|----|----|----|----|

| Bit number    | 31 30 29               | 28 27 26                 | 25 2   | 4 23 2    | 2 21   | 20    | 19    | 18    | 17    | 16          | 15 14  | 13    | 12 1 | 1 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Initial state |                        | -                        |        |           |        |       |       |       |       |             | -      |       |      |   | —  | -  | —  | _  | _  | —  | -  | —  | —  | -  | —  |