# РУКОВОДСТВО ПО ЭКСПЛУАТАЦИИ Мультиклеточный процессор MultiClet R1

Mультиклеточные процессоры: MCp042R100102-LQ256

#### Аннотация

Микропроцессор MCp042R100102-LQ256 имеет в своем составе мультиклеточное процессорное ядро. Ядро МП содержит 4 клетки - когерентных процессорных блоков, объединенных интеллектуальной коммутационной средой. МП имеют динамически реконфигурируемое ядро, распределение вычислительных ресурсов (клеток) по задачам производится согласно алгоритму заложенному в исполняемой программе. При этом один и тот же код может выполняться любым количеством и комбинацией клеток. Мультиклеточный процессор предназначен для решения широкого круга задач управления и цифровой обработки сигналов в приложениях, требующих минимального энергопотребления и высокой производительности.

#### Особенности:

- Число клеток 4

- Разрядность процессора 32/64 бита

- ПП(на кристалле) 256 Кбайт

- ПД(на кристалле)  $256~{

m Kбайт}$

- блок операций над числами с плавающей запятой (в каждой клетке)

- Тактовая частота до 100 МГц;

- Производительность процессора 24 FLOPS/МГц;

#### Общие характеристики:

- Kopπyc LQFP-256

- Условия эксплуатации (-60 ...+125°C)

- Максим. потребл. мощность:

- ядра 1,05Вт на частоте 100МГц

- выходных каскадов портов 80мВт

- Напряжение питания (раздельное): ядра 1,8В, выходных каскадов — 3,3В

#### Периферийные устройства:

- 2 интерфейса SPI с селектором «ведомых» устройств (в режиме «ведущий»)

- 4 универсальных асинхронных приёмопередатчика UART с FIFO на прием/передачу

- 2 интерфейса I2C (один «ведомый» и один «ведущий»)

- интерфейс I2S («ведомый»/ «ведущий»)

- Ethernet MAC контроллер 10/100Mб/с

- USB 2.0 HS (device), внешний интерфейс ULPI

- часы реального времени с календарем

- 4 таймера общего назначения

- 6 портов ввода-вывода, общее количество вводов-выводов – 166

- 4-х канальный контроллер ШИМ

- сторожевой таймер

- АЦП(16 бит, 48 Квыб/с, 8 каналов)

- ЦАП(12 бит, 100 Мвыб/с, 1 канал)

# Содержание

www.multiclet.com

| 1 | 1.1 |        | ж сокращений                            |   |

|---|-----|--------|-----------------------------------------|---|

|   | 1.2 |        | ятые условные обозначения               |   |

| 2 | Опт | исание |                                         |   |

| _ | 2.1 |        | яные технические характеристики         |   |

|   | 2.1 |        | ктура МП                                |   |

|   | 2.2 | Струг  | riypa Mili                              | T |

| 3 | Цен | траль  | ное процессорное устройство             | 1 |

|   | 3.1 | Орган  | изация вычислительного процесса         | 1 |

|   | 3.2 | Механ  | низмы реализации                        | 1 |

|   |     | 3.2.1  | Идентификация команд                    | 1 |

|   |     | 3.2.2  | Организация буфера команд               | 1 |

|   |     | 3.2.3  | Управление коммутационной средой        | 2 |

|   | 3.3 | Струк  | ктура и организация клетки              | 2 |

|   |     | 3.3.1  | Устройство выборки команд               | 2 |

|   |     | 3.3.2  | Устройство управления                   | 2 |

|   |     | 3.3.3  | Буфер команд                            | 2 |

|   |     | 3.3.4  | Коммутационное устройство               | 2 |

|   |     | 3.3.5  | Целочисленное АЛУ                       | 2 |

|   |     | 3.3.6  | АЛУ с плавающей точкой                  | 2 |

|   |     | 3.3.7  | Блок доступа к памяти данных            | 2 |

|   |     | 3.3.8  | Мультиплексор результатов               | 2 |

|   |     | 3.3.9  | Набор регистров                         | 2 |

|   |     | 3.3.10 | Контроллер прерываний и отладочный блок | 2 |

|   | 3.4 | Регис  | тры                                     | 2 |

|   | 3.5 | Контр  | ооллер прерываний                       | 3 |

|   |     | 3.5.1  | Структура контроллера прерываний        | 3 |

|   |     | 3.5.2  | Регистры контроллера прерываний         | 3 |

|   |     | 3.5.3  | Порядок обработки прерываний            | 3 |

|   | 3.6 | Систе  | мный таймер                             | 3 |

|   |     | 3.6.1  | Режимы работы                           | 3 |

|   |     |        |                                         |   |

| 4 | Сре | едства | динамической реконфигурации             | 4 |

| 5 | Орі | ганиза | ция памяти                              | 4 |

|   | -   |        |                                         |   |

Все права защищены  $\bigcirc$  OAO «Мультиклет» 2010-2015

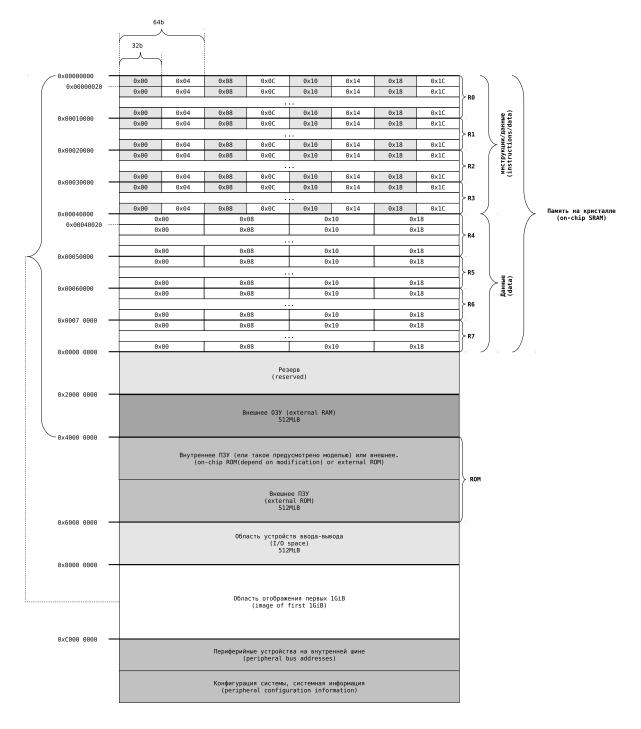

|   | 5.1 | Карта   |                                                               | 43 |

|---|-----|---------|---------------------------------------------------------------|----|

|   | 5.2 | Комм    | утатор                                                        | 46 |

|   | 5.3 | Контр   | ооллер транзакций данных (DTC)                                | 49 |

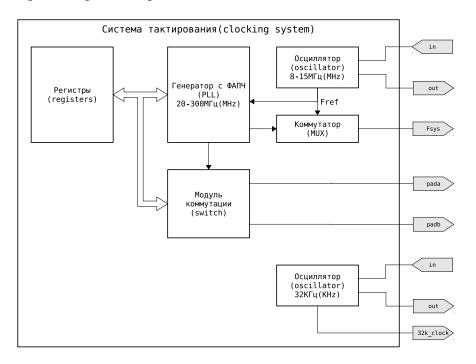

| 6 | Сис | стема : | гактирования                                                  | 52 |

|   |     | 6.0.1   | Описание работы системы тактирования                          | 52 |

|   |     | 6.0.2   | Описание работы модуля коммутации                             | 53 |

|   |     | 6.0.3   | Таблицы выбора коэффициентов R, N, K                          | 54 |

|   |     | 6.0.4   | Порядок работы с блоком PLL                                   | 54 |

|   |     | 6.0.5   | Регистры системы тактирования                                 | 56 |

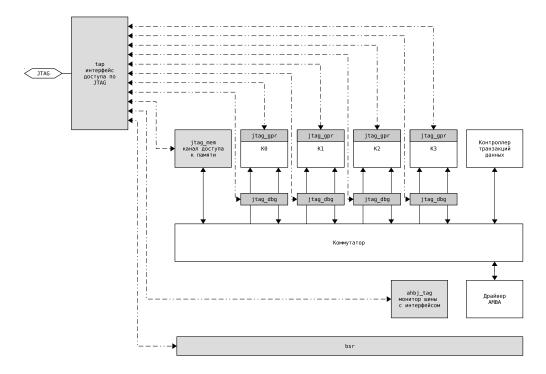

| 7 | Апі | ларатн  | ая система отладки и тестирования                             | 59 |

|   | 7.1 | Контр   | ооллер (tap)                                                  | 59 |

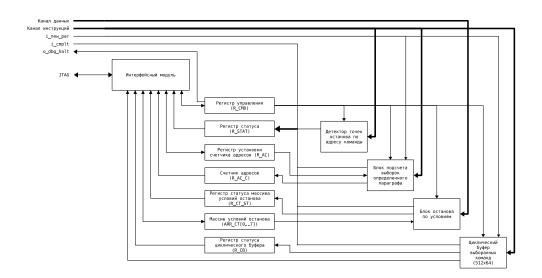

|   | 7.2 | Канал   | ı доступа к памяти (jtag_mem)                                 | 61 |

|   | 7.3 | Канал   | и доступа к регистрам общего назначение и регистрам системной |    |

|   |     | периф   | рерии (jtag_gpr)                                              | 62 |

|   | 7.4 | Канал   | ı доступа к устройствам на шине АМВА (ahb_jtag)               | 63 |

|   | 7.5 | Модул   | ть отладки ПО (jtag_dbg)                                      | 65 |

|   | 7.6 | Регис   | тр периферийного сканирования (bsr)                           | 70 |

| 8 | Пер | оифері  | ийные устройства                                              | 71 |

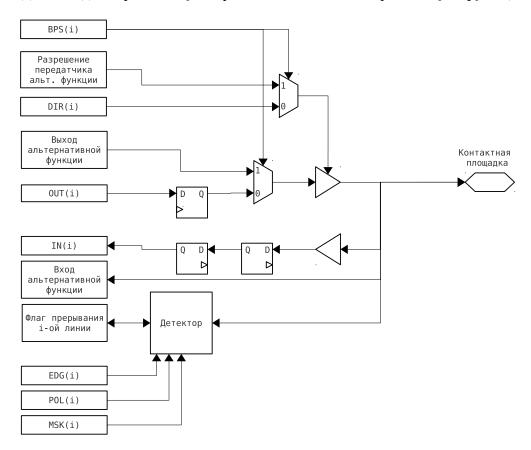

|   | 8.1 | Порт    | ввода-вывода (GPIO)                                           | 72 |

|   |     | 8.1.1   | Краткие характеристики                                        | 72 |

|   |     | 8.1.2   | Функционирование GPIO                                         | 72 |

|   |     | 8.1.3   | Описание регистров                                            | 74 |

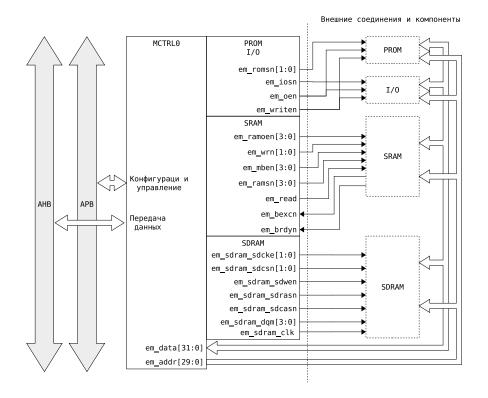

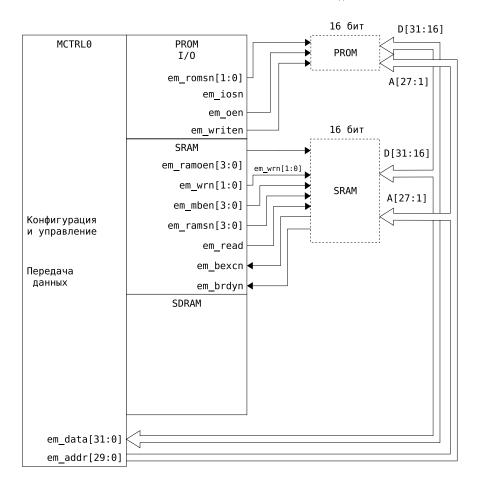

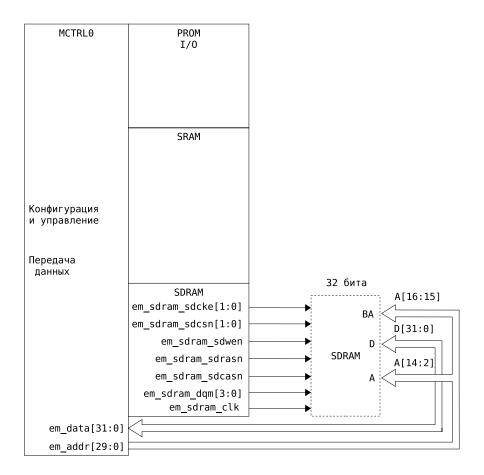

|   | 8.2 | Контр   | ооллер шины внешней памяти (MCTRL0)                           | 76 |

|   |     | 8.2.1   | Краткие характеристики                                        | 76 |

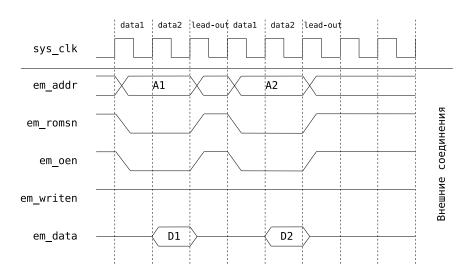

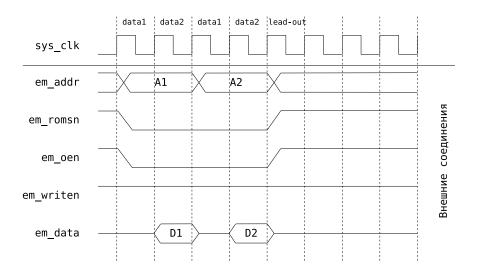

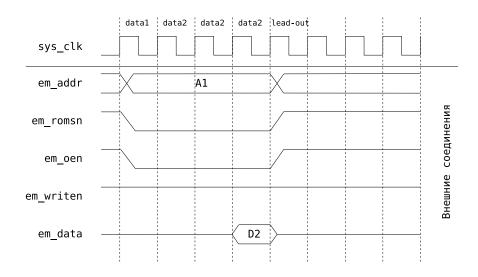

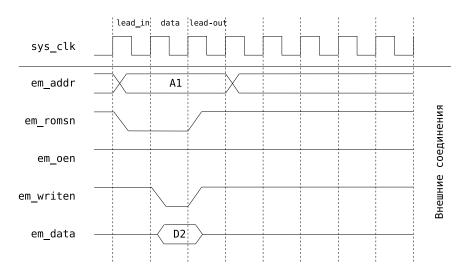

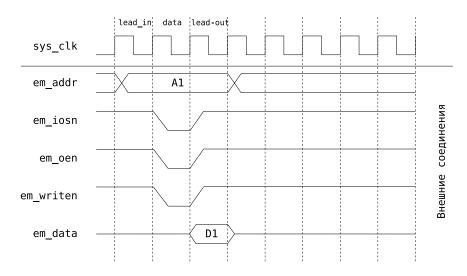

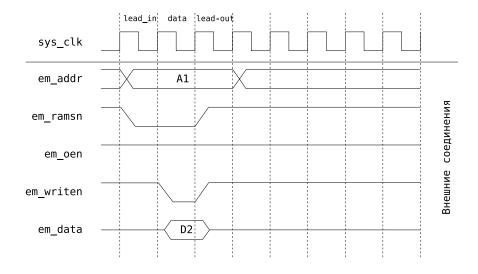

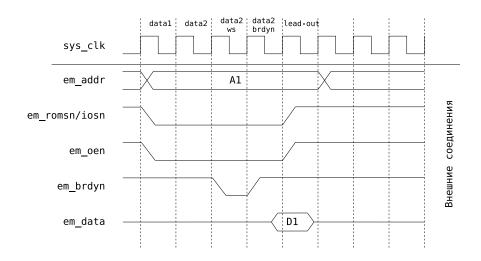

|   |     | 8.2.2   | Интерфейс PROM                                                | 77 |

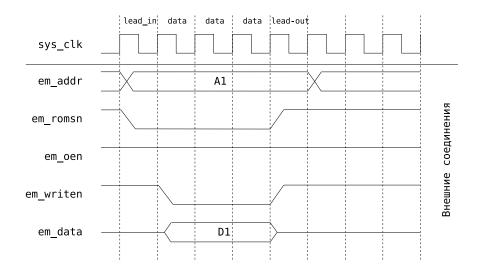

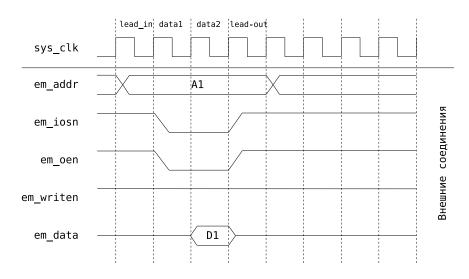

|   |     | 8.2.3   | Интерфейс I/O                                                 | 80 |

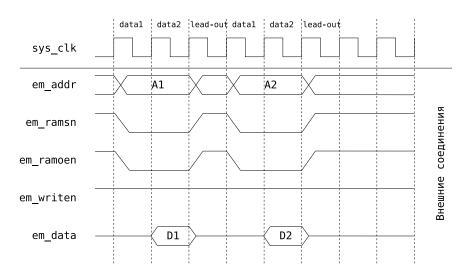

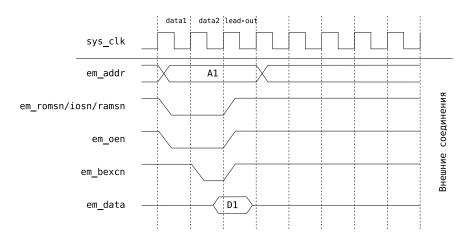

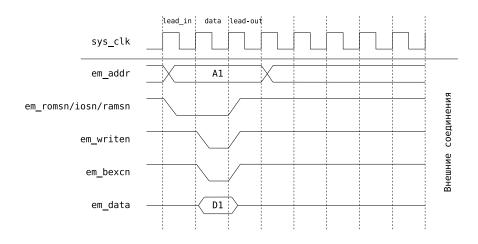

|   |     | 8.2.4   | Интерфейс SRAM                                                | 82 |

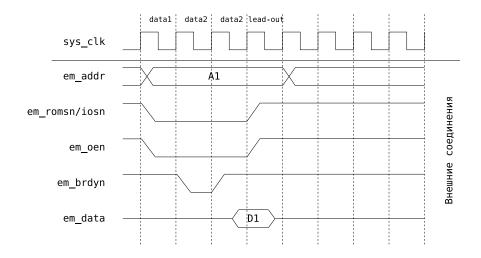

|   |     | 8.2.5   | Интерфейс SDRAM                                               | 84 |

|   |     | 8.2.6   | Использование сигнализации готовности шины                    | 87 |

|   |     | 8.2.7   | Ошибки доступа                                                | 88 |

|   |     | 8.2.8   | Подключение PROM, SRAM, SDRAM памяти различной разряд-        |    |

|   |     |         | ности                                                         | 89 |

|   |     | 8.2.9   | Описание регистров                                            | 92 |

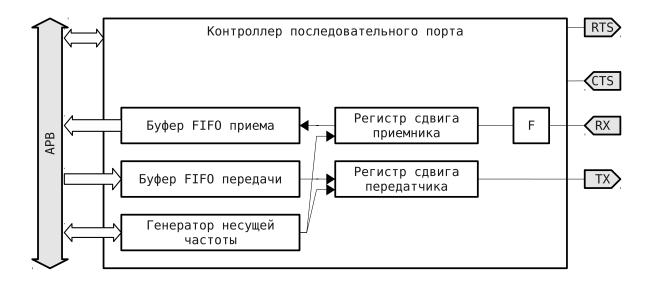

|   | 8.3 | Интер   | офейс UART(UARTx)                                             | 95 |

|   |     | 8.3.1   | Краткие характеристики                                        | 95 |

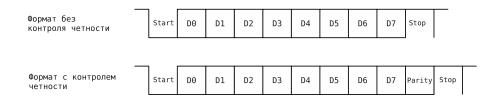

|     | 8.3.2 | Передача данных                                             | 95  |

|-----|-------|-------------------------------------------------------------|-----|

|     | 8.3.3 | Прием данных                                                | 97  |

|     | 8.3.4 | Установка скорости передачи                                 | 98  |

|     | 8.3.5 | Режимы самотестирования                                     | 98  |

|     |       | 8.3.5.1 Режим самотестирования на уровне интерфейсных линий | 98  |

|     |       | 8.3.5.2 Режим самотестирования на уровне данных             | 98  |

|     | 8.3.6 | Формирование прерываний                                     | 98  |

|     |       | 8.3.6.1 Режим отложенных прерываний приемника               | 99  |

|     | 8.3.7 | Описание регистров                                          | 100 |

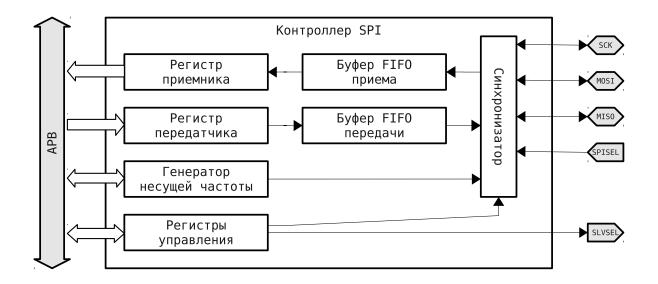

| 8.4 | Интер | офейс SPI(SPIx)                                             | 102 |

|     | 8.4.1 | Краткие характеристики                                      | 102 |

|     | 8.4.2 | Трех-проводный режим                                        | 104 |

|     | 8.4.3 | Прием и передача данных                                     | 104 |

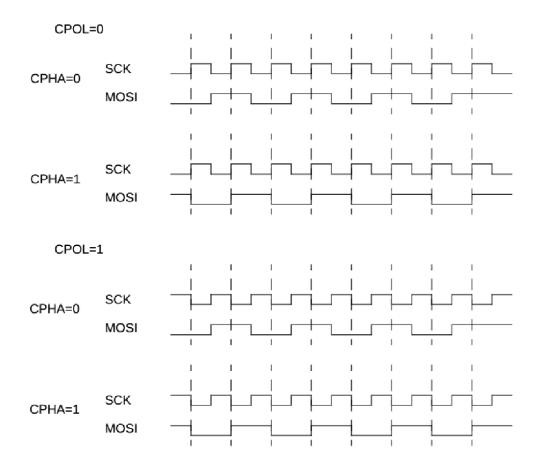

|     | 8.4.4 | Тактовый сигнал SCK                                         | 104 |

|     | 8.4.5 | Работа в режиме «ведущий»                                   | 104 |

|     | 8.4.6 | Работа в режиме «ведомый»                                   | 105 |

|     | 8.4.7 | Описание регистров                                          | 106 |

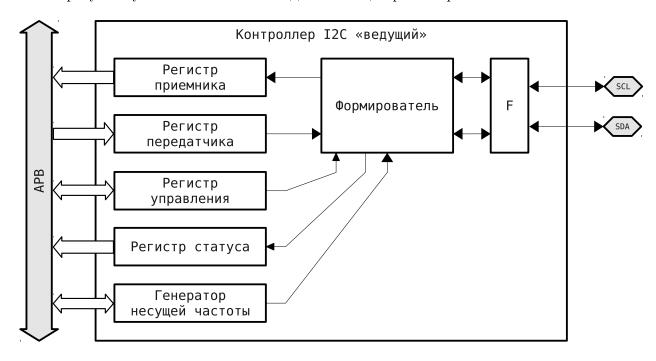

| 8.5 | Интер | офейс $I^2C$ «ведущий» (I2C0)                               | 109 |

|     | 8.5.1 | Краткие характеристики                                      | 109 |

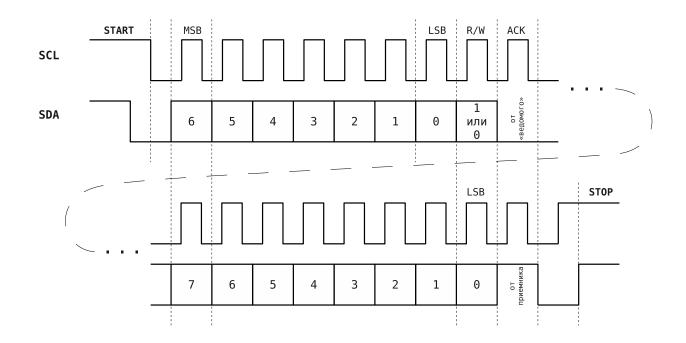

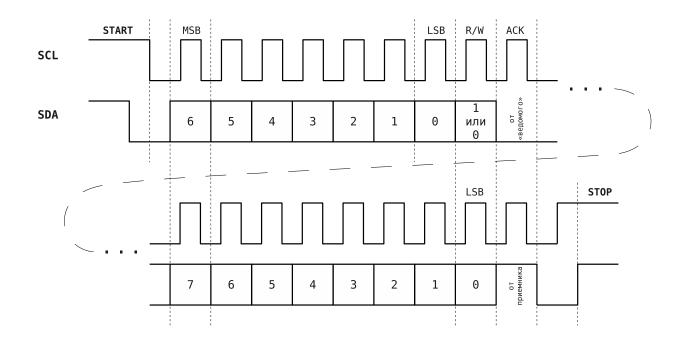

|     | 8.5.2 | Общее описание протокола приема-передачи                    | 110 |

|     | 8.5.3 | Генерация несущей частоты                                   | 111 |

|     | 8.5.4 | Алгоритм работы с интерфейсом                               | 111 |

|     |       | 8.5.4.1 Запись данных                                       | 112 |

|     |       | 8.5.4.2 Чтение данных                                       | 112 |

|     | 8.5.5 | Описание регистров                                          | 114 |

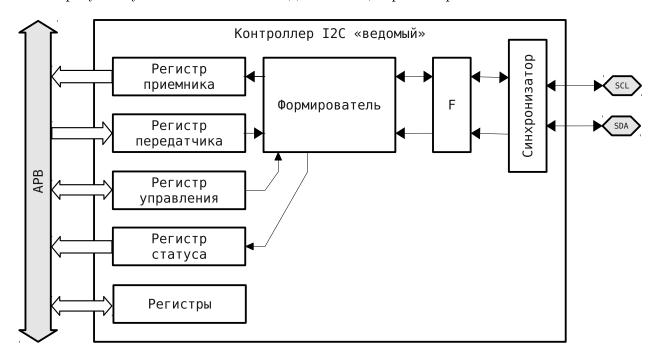

| 8.6 | Интер | офейс $I^2C$ «ведомый» (I2C1)                               | 116 |

|     | 8.6.1 | Краткие характеристики                                      | 116 |

|     | 8.6.2 | Общее описание протокола приема-передачи                    | 117 |

|     | 8.6.3 | Генерация несущей частоты                                   | 118 |

|     | 8.6.4 | Алгоритм работы с интерфейсом                               | 118 |

|     |       | 8.6.4.1 Прием данных от «ведущего»                          | 118 |

|     |       | 8.6.4.2 Передача данных «ведущему»                          | 119 |

|     | 8.6.5 | Описание регистров                                          | 120 |

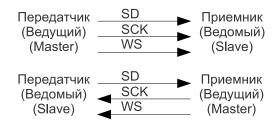

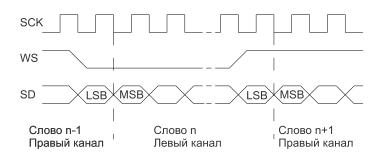

| 8.7 | Контр | роллер $I^2S(\mathrm{I2Sx})$                                | 122 |

|     | 8.7.1 | Краткие характеристики                                      | 122 |

|     | 8.7.2 | Общее описание шины $I^2S$                                  | 122 |

|     | 8.7.3 | Особенности текушей реализации $I^2S$                       | 123 |

|      | 8.7.4   | Описание регистров                                            | 124 |

|------|---------|---------------------------------------------------------------|-----|

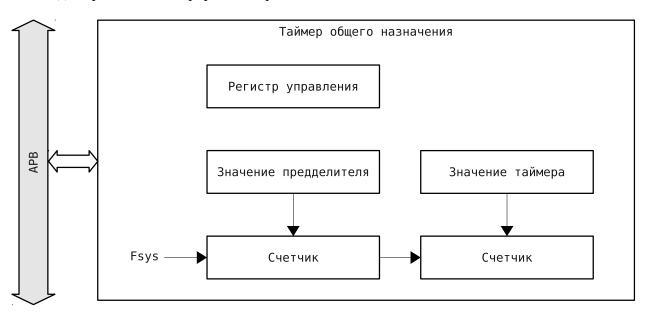

| 8.8  | Тайме   | р общего назначения(GPTIMx)                                   | 126 |

|      | 8.8.1   | Краткие характеристики                                        | 126 |

|      | 8.8.2   | Алгоритм работы                                               | 126 |

|      | 8.8.3   | Описание регистров                                            | 128 |

| 8.9  | Контр   | оллер Ethernet(Ethernet0)                                     | 130 |

|      | 8.9.1   | Краткие характеристики                                        | 130 |

|      | 8.9.2   | Тактирование                                                  | 130 |

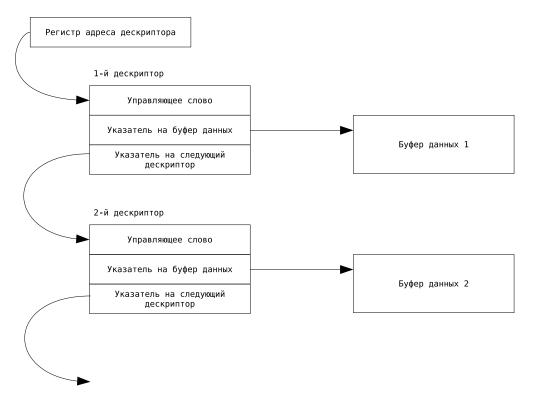

|      | 8.9.3   | КПДП передатчика                                              | 131 |

|      |         | 8.9.3.1 Установка дескриптора                                 | 131 |

|      |         | 8.9.3.2 Подготовка данных для передачи                        | 131 |

|      |         | 8.9.3.3 Передача данных                                       | 132 |

|      |         | 8.9.3.4 Работа с дескриптором после окончания передачи данных | 132 |

|      | 8.9.4   | КПДП приемника                                                | 132 |

|      |         | 8.9.4.1 Установка дескриптора                                 | 133 |

|      |         | 8.9.4.2 Прием данных                                          | 133 |

|      |         | 8.9.4.3 Работа с дескриптором после окончания приема данных . | 134 |

|      |         | 8.9.4.4 Ошибки приема на шине АНВ                             | 134 |

|      |         | 8.9.4.5 Допустимые МАС адреса                                 | 134 |

|      | 8.9.5   | MDIO интерфейс                                                | 135 |

|      |         | 8.9.5.1 Прерывания РНҮ                                        | 135 |

|      | 8.9.6   | Описание регистров                                            | 136 |

| 8.10 | Контр   | оллер USB(USBx)                                               | 139 |

|      | 8.10.1  | Краткие характеристики                                        | 139 |

|      | 8.10.2  | Обзор системы                                                 | 140 |

|      | 8.10.3  | РНҮ интерфейс                                                 | 141 |

|      | 8.10.4  | Speed Negotiation Engine(SNE)                                 | 141 |

|      | 8.10.5  | Serial Interface Engine(SIE)                                  | 141 |

|      | 8.10.6  | Буферы конечной точки                                         | 141 |

|      | 8.10.7  | AMBA Interface Engine(AIE)                                    | 142 |

|      | 8.10.8  | Синхронизация                                                 | 142 |

|      | 8.10.9  | Формирование сброса                                           | 142 |

|      | 8.10.10 | ПДП операции                                                  | 142 |

|      | 8.10.11 | Конечные точки типа OUT                                       | 143 |

|      | 8.10.12 | Конечные точки типа IN                                        | 145 |

|      | 8.10.13 | Конечные точки                                                | 146 |

|      | 8.10.14 | Управляющие конечные точки                                    | 146 |

|              |      | $8.10.15\Pi$ акетные конечные точки              | 146 |

|--------------|------|--------------------------------------------------|-----|

|              |      | 8.10.16 Конечные точки по прерываниям            | 146 |

|              |      | 8.10.17 Изохронные конечные точки                | 146 |

|              |      | 8.10.18 Описание регистров                       | 147 |

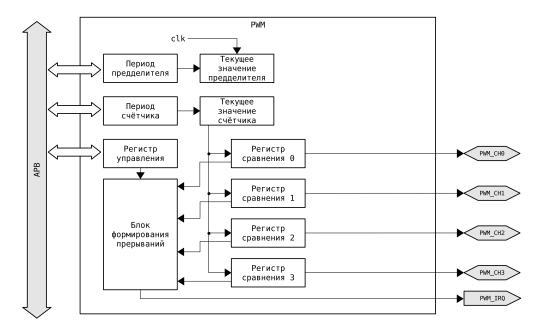

|              | 8.11 | Контроллер PWM(PWMx)                             | 151 |

|              |      | 8.11.1 Краткие характеристики                    | 151 |

|              |      | 8.11.2 Инициализация ШИМ                         | 151 |

|              |      | 8.11.3 Режимы работы ШИМ                         | 152 |

|              |      | 8.11.4 Прерывания ШИМ                            | 152 |

|              |      | 8.11.5 Длительность импульса ШИМ                 | 152 |

|              |      | 8.11.6 Описание регистров                        | 153 |

|              | 8.12 | Часы реального времени RTC                       | 155 |

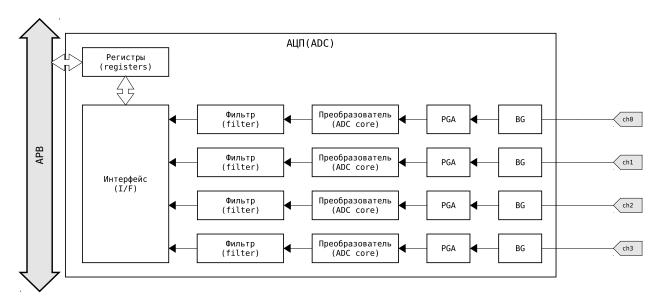

|              | 8.13 | Аналого-цифровой преобразователь(ADCx)           | 156 |

|              |      | 8.13.1 Краткие характеристики                    | 156 |

|              |      | 8.13.2 Описание регистров                        | 158 |

|              | 8.14 | Цифро-аналоговый преобразователь(DACx)           | 160 |

|              |      | 8.14.1 Краткие характеристики                    | 160 |

|              |      | 8.14.2 Описание регистров                        | 161 |

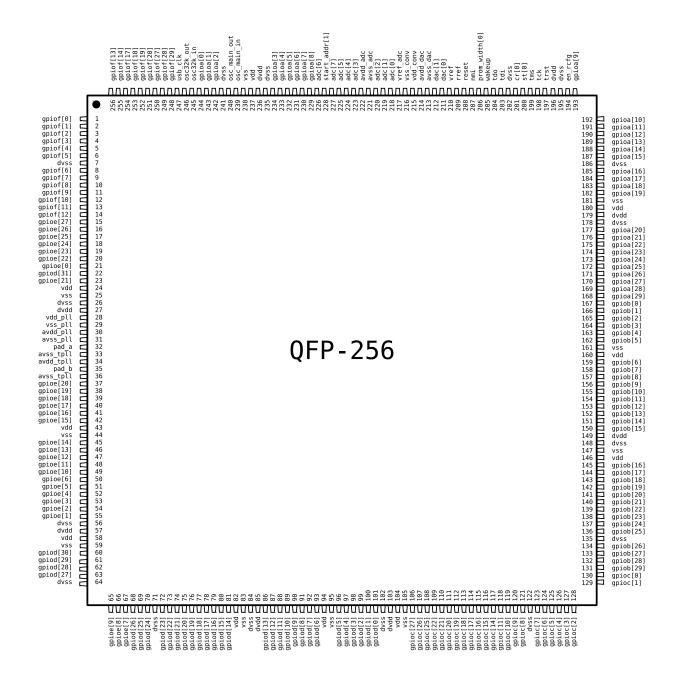

| 9            | Наз  | начение выводов процессора                       | 162 |

|              | 9.1  | Назначение выводов процессора в корпусе QFP256   | 162 |

|              | 9.2  | Диаграмма выводов процессора в корпусе QFP256    | 168 |

| 10           | Эле  | ектрические параметры                            | 169 |

|              | 10.1 | Электрические характеристики портов ввода-вывода | 169 |

| 11           | Лис  | ст регистрации изменений                         | 171 |

| $\mathbf{A}$ | При  | иложение. Руководство по применению              |     |

|              | сло  | жно-функциональных блоков(СФБ) «GAISLER»         | 172 |

# 1 Условные обозначения и сокращения

## 1.1 Список сокращений

```

СФБ — сложно-функциональный блок;

M\Pi — микропроцессор;

\Pi O — программное обеспечение;

MSb — старший значащий бит;

MSB — старший значащий байт;

LSb — младший значащий бит;

LSB — младший значащий байт;

ОЗУ — оперативное запоминающее устройство;

\Pi Y — периферийное устройство;

\Pi\PiУ — центральное процессорное устройство;

ФБО — физический блок ОЗУ;

\Pi\Pi — память программ;

\Pi Д — память данных;

ФНЧ — фильтр нижних частот;

КДВП — контроллер доступа к внешней памяти;

\Pi \Pi \Pi — прямой доступ к памяти;

РОН — регистр(ы) общего назначения;

```

# 1.2 Принятые условные обозначения

'1', '0'— состояние логической единицы, логического нуля, соответственно;

REG(BIT) — такая запись используется для указания бита в регистре, где REG - название регистра, а BIT - обозначение бита или группы битов в нем. Например, "бит I2CxCR(EN)" означает, что идет указание на бит EN регистра I2CxCR, а

"I2CxPSC(PSC)" указывает на группу битов PSC. Что бы подробнее узнать об указанных регистрах и битах, надо смотреть описание этих регистров;

PUx, BLOCKx, PUxREG — В обозначении регистров, наименовании ПУ, блоков МП может использоваться символ "x". Это замещение номера, например, есть несколько идентичных периферийных блоков UART с номерами 0,1 и т.д. Для UART0 "x" - 0. Если есть регистр I2CxCR, то для блока I2C0, регистр будет именоваться I2C0CR.

www.multiclet.com UM HDL50002 Rev:101 09.07.2015 8-172

# 2 Описание

# 2.1 Основные технические характеристики

| Условное обозначение                                            | m MCp042R100102-LQ256              |

|-----------------------------------------------------------------|------------------------------------|

| Основное функциональное назначение                              | 64-разрядная микро-ЭВМ             |

| Максимальная тактовая частота ядра, МГц                         | 100                                |

| Мультиклеточное ядро                                            | 4 клетки 32/64 разряда             |

| Блок вычисления чисел с плавающей точкой(соответствует ieee754) | двойной точности                   |

| Производительность пиковая                                      | 24 MFLOPS/MΓц                      |

| Встроенная память СОЗУ, Кбайт                                   | 512                                |

| Внешняя шина памяти, бит                                        | 32                                 |

| Внешняя шина памяти, типы памяти                                | PROM, SRAM, SDRAM, IO              |

| USB 2.0 HS device, mt.                                          | 1                                  |

| UART, mt.                                                       | 4                                  |

| SPI, mt.                                                        | 2                                  |

| I2C                                                             | 1 ведущий, 1 ведомый               |

| I2S                                                             | 1 ведущий/ведомый (прием/передача) |

| PWM, каналов                                                    | 4                                  |

| Ethernet 10/100, mt.                                            | 1                                  |

| ЦАП, 12 бит, 125Msps, каналов                                   | 1                                  |

| АЦП, 16 бит, 48Ksps, каналов                                    | 8                                  |

| Пользовательские вводы-выводы, шт.                              | 159                                |

# 2.2 Структура МП

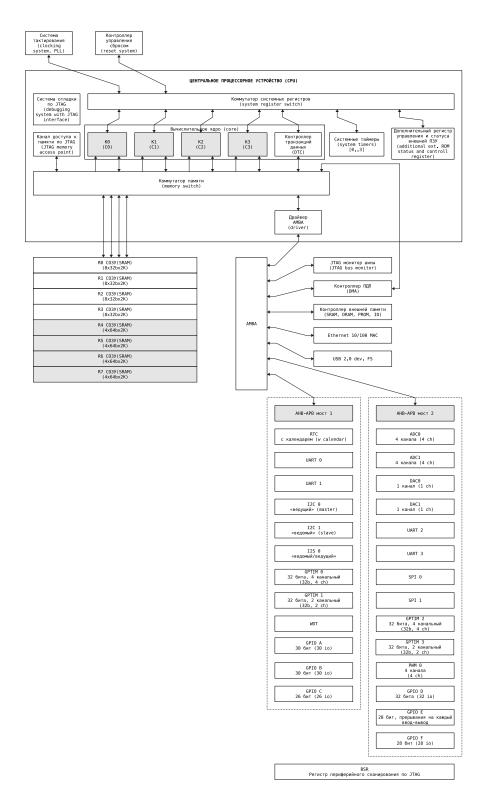

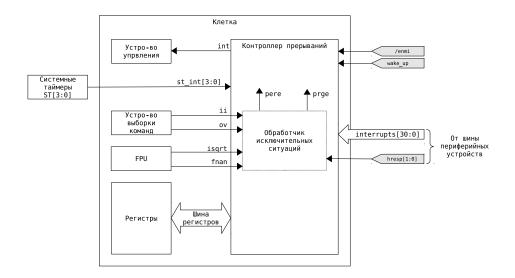

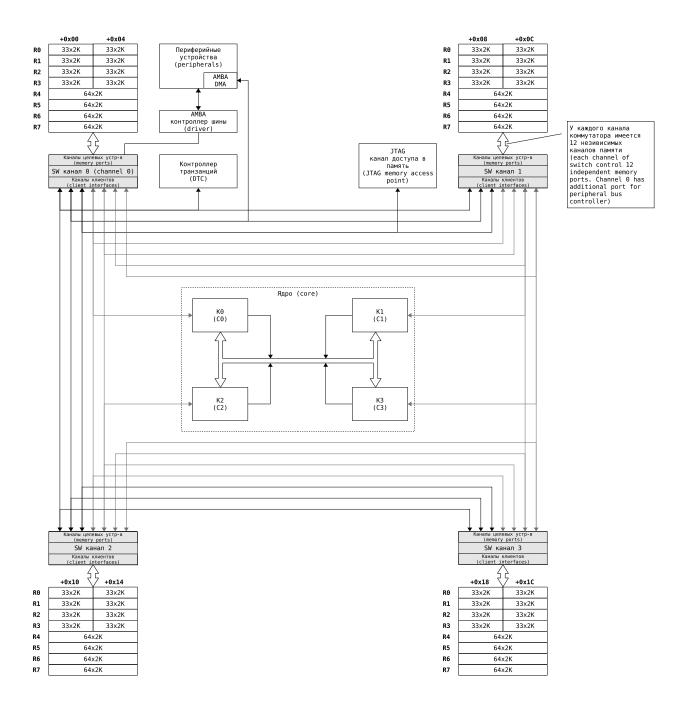

Рис. 1: Общая структура МП

## МП имеет следующие основные части:

- центральное процессорное устройство (ЦПУ);

- периферийные устройства. В качестве шины периферийных устройств используется шина AMBA 2.0;

- оперативные запоминающие устройства типа СОЗУ.

# 3 Центральное процессорное устройство

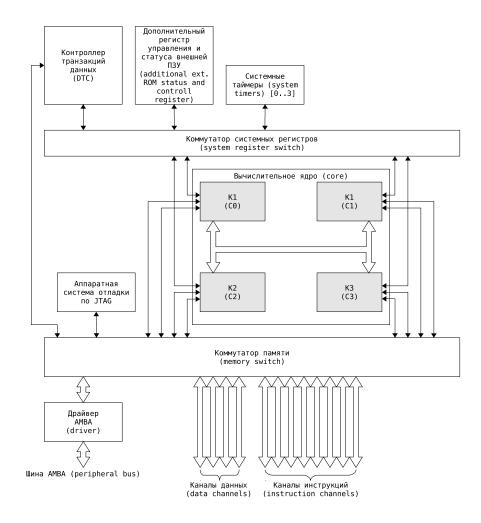

Рис. 2: Структурная схема ЦПУ

## ЦПУ в своем составе имеет:

- 4-х клеточное вычислительное ядро;

- коммутатор памяти;

- системные устройства;

- коммутатор системных регстров;

- аппаратную систему отладки ПО.

Структурная схема ядра микропроцессора представлена на рис. 2

## 3.1 Организация вычислительного процесса

Исполнение процессором любой команды завершается формированием некоторого результата. Использование этого результата последующими исполняемыми командами, образует информационную связь между командой–источником результата и командами–приемниками этого результата. Эта информационная связь может быть как прямой, так и косвенной.

Абсолютно все современные цифровые процессоры, кроме мультиклеточных, используют косвенную связь, при которой результат доступен только после его отчуждения. Возможно всего два способа реализации этой связи.

Первый – запись его командой-источником в общедоступные регистры и/или память, имя которых при использовании задают в поле операнда команды—приемника (фоннеймановская модель процессора). Как следствие, решение задачи подобным процессором достигается пошаговым целенаправленным изменением состояния вычислительной системы. Этот процесс изменения состояний диктуется исполнением последовательности команд строго в заданном порядке, который определяют в процессе программирования.

Второй – адресная рассылка, т.е. запись его в память по адресу в который, при программировании, должна быть помещена команда-приемник (потоковые процессоры). Типичная команда потокового процессора, например, двухместная арифметическая операция, содержит, как правило, поле кода операции, поля двух операндов, одно или несколько полей адресов команд, которым передается результат выполненной операции, и, соответственно, поля номеров операндов, в которых он будет размещен. Команда выбирается и выполняется «по готовности операндов», т.е. тогда, когда в ее поля операндов будут записаны все результаты выполнения других команд, необходимые для ее выполнения. Таким образом, команды в программе могут быть размещены произвольным образом. Принцип исполнения команд потокового процессора «по готовности операндов» позволяет реализовать параллелизм «естественным» образом, т.е. без необходимости решения задачи распараллеливания.

Принципиально иной вид информационной связи между командами – это прямая связь. В этом случае команды именуются и при этом имена должны идентифицировать собственно команду, а не ее местоположение или другие особенности реализации. Доступ к результатам может осуществляться по именам как команд—источников, так команд—приемников. В первом случае используется широковещательная рассылка с последующим поименным отбором, при которой в поле операнда команды—приемника

задают имя команды-источника. Во втором – выполняется поименная рассылка, при которой в команде-источнике задают имя (имена) команды-приемника результата.

Известным примером кодирования программы с использованием прямых информационных связей между командами является язык триад, используемый в качестве промежуточного представления исходной программы в процессе компиляции.

Промежуточное представление в виде триад образуется записями с тремя полями: <op><arg1><arg2>,

где: op – поле кода операции; arg1 – поле первого операнда; arg2 – поле второго операнда.

В качестве операндов используются это либо указатели на таблицу символов (для имен, определенных программистом, или констант), либо указатели на триады—источники используемых результатов. Для следующей последовательности операторов, написанной на языке высокого уровня и образующей линейный участок:

```

L1: a:=b+c;

i:=a*f-g;

a:=i/h;

goto L2;

```

промежуточное представление на языке триад будет выглядеть так, как показано в таблице 1:

Номер триады op arg1 arg2 0 +b \* (0)1 f 2 (1) g 3 (2) h 4 (2)

:=

goto

(3)

a

L2

5

6

Таблица 1.

Имена – это указатели на таблицу символов, а числа в скобках – это указатели (ссылки) на триады.

Развитием языка триад является представление программы в контекстно-зависимом виде, при котором она делится на совокупность параграфов. Внутри параграфа информационная связь между его командами только прямая. При этом команды параграфа

образуют частично упорядоченную и информационно замкнутую линейную последовательность, а именно, команды—источники предшествуют своим командам-приемникам, а команды—приемники имеют ссылки только на команды-источники своего параграфа. Соответственно, информационная связь между командами различных параграфов косвенная, через память.

Ссылки кодируются числом, значение которого равно разнице между номерами командыприемника и команды-источника, полученными при последовательной нумерации команд параграфа. Так, например, фрагмент программы, приведенный в таблице 1, будет выглядеть следующим образом (см. таблицу 2).

Таблица 2.

| Номер триады | op               | arg1 | arg2 |

|--------------|------------------|------|------|

| 0            | rd               |      | b    |

| 1            | $_{ m rd}$       |      | С    |

| 2            | $_{\mathrm{rd}}$ |      | f    |

| 3            | $_{\mathrm{rd}}$ |      | g    |

| 4            | $_{\mathrm{rd}}$ |      | h    |

| 5            | +                | 5    | 4    |

| 6            | *                | 1    | 4    |

| 7            | -                | 1    | 4    |

| 8            | /                | 1    | 4    |

| 9            | :=               | 2    | 4    |

| 10           | :=               | 2    | i    |

| 11           | goto             | L2   | a    |

Последнюю команду параграфа отмечают управляющим признаком «конец параграфа». Максимальное значение ссылки (окно видимости результата исполненной команды) определяется размером ее поля в команде и равно 2\*p-1, где p – размер поля ссылки в битах.

Основные особенности контекстно-зависимой программы, которые определяют организацию вычислительного процесса и аппаратную реализацию ядра мультиклеточного процессора следующие:

Во-первых, последовательность команд имеет линейный характер, а каждая команда имеет свой номер. Следовательно, по номеру команды и по значениям ссылок можно определить номера команд, результаты которых необходимы данной команде. Необходимым условием этого является упорядоченная выборка команд.

Во-вторых, информационные связи между командами указаны явно, что позволяет организовать исполнение команд по готовности операндов и таким образом обеспечить

естественную реализацию параллелизма. При этом необходимо обеспечить хранение уже выбранной команды до момента ее исполнения и сохранность полученного результата до его передачи командам-приемникам, если они еще не выбраны.

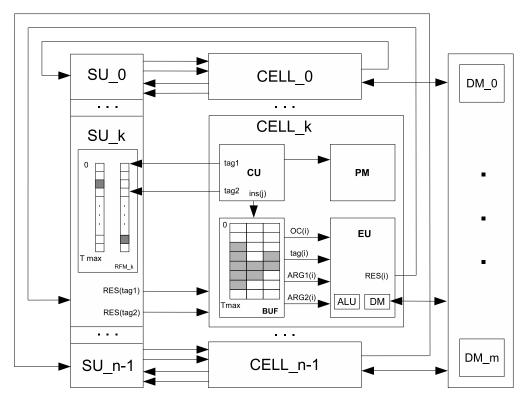

В третьих, естественная реализация параллелизма предполагает использование нескольких процессорных устройств. Так как исполняемая команда не имеет информации о потребителях получаемых результатов, ее результаты должны рассылаться всем потенциальным потребителям, а команды-приемники должны отбирать требуемые им результаты из общего потока. Ядро мультиклеточного процессора, учитывающее эти особенности, состоит из совокупности идентичных процессорных блоков (клеток), объединённых однонаправленной полносвязной коммутационной средой (SB). Каждая клетка включает устройство управления (CU), буфер команд (BUF) и набор исполнительных устройств (EU). Обобщенная структура ядра мультиклеточного процессора приведена на рис.3.

Рис. 3: Обобщенная структура ядра мультиклеточного процессора

Процесс исполнения команды включает три этапа:

- 1. выборки командных слов;

- 2. отбор результатов;

- 3. исполнения команд.

www.multiclet.com UM HDL50002 Rev: 101 09.07.2015 16-172

Выборка командных слов осуществляется устройством управления. При этом выполняются следующие действия:

Начиная с первой команды очередного параграфа, устройства управления всех клеток группы мультиклеточного процессора, совместно исполняющей программу (task-группа), синхронно выбирают и декодируют группу последовательно размещенных команд выполняемого параграфа. При этом первая клетка группы выбирает первую команду последовательности, вторая — вторую и т.д. Если среди выбранных команд есть команда с признаком «конец параграфа», то последующие выбранные команды группы считаются невалидными и не декодируются.

При декодировании каждой команде присваивается индивидуальная идентификационная метка (тег), вычисляются теги команд, результаты которых являются операндами декодируемой команды, формируется и передается запрос коммутатору на отбор этих результатов из их общего потока.

Если все клетки группы готовы к приему очередной команды, то декодируемая команда записывается в буфер команд, коммутатор запоминает запрос и выборка повторяется.

Готовность клеток к приему может определяться целым рядом факторов, например, занятостью тега, буфера команд и т.п. Процесс выборки может также приостанавливаться если после выборки последней команды параграфа не известен адрес следующего параграфа. Он возобновляется после его формирования.

Отбор результатов выполняется коммутатором, который состоит из совокупности коммутационных устройств (SU), каждое из которых обслуживает одну клетку. Коммутационное устройство принимает запросы на отбор результатов, запоминает их теги в памяти запросов (RFM) и если среди уже поступивших результатов есть те, значение тегов которых записано в RFM, передает их в буфер команд. В RFM соответствующая отметка убирается (запрос выполнен).

Процесс исполнения команды инициализируется, если в буфере команд есть хотя бы одна команда, у которой получены все операнды. При этом, если готовых к исполнению команд несколько, то выбирается, как правило, команда, которая была записана в буфер раньше всех, и эта команда передается в операционное устройство. Операционное устройство выполняет команду и выдает во все коммутационные устройства клеток своей task-группы её результат с тегом, равным тегу команды. Приостанавливается этот процесс тогда, когда в буфере нет готовых к исполнению команд.

## 3.2 Механизмы реализации

## 3.2.1 Идентификация команд

Известно, что любая команда выполняется за конечное число тактов и, если в качестве тега использовать некоторое число, то через определенное время это значение будет свободно и оно может быть присвоено очередной выбираемой команде. Очевидно также, что для того чтобы определить значение, которым идентифицируются запрашиваемые результаты необходимо чтобы значения тегов образовывали последовательность и присваивались в порядке размещения команд. А именно, тег очередной команды должен быть на единицу больше тега предыдущей команды. А их общее количество (Tmax) должно быть не менее окна видимости, чтобы обеспечить гарантированное отсутствие блокировки. Таким образом, тег i-ой команды при выборке ее i-ой клеткой может быть представлен как  $tag(i):=(tag(i-k)+k)mod\ Tmax$ , где: k – количество клеток в группе. Ограничение ширины окна выбранных команд требует запоминания состояния значения метки (занято, незанято) для того чтобы обеспечить возможность повторного использования значения тега. Механизмом, управляющим процессом назначения тегов и обеспечивающим приостановку процесса выборки при занятости значения служит память занятых тегов (BTM).

Сопоставим каждому значению тега бит, который равен единице, если это значение занято, и нулю, если оно свободно. Бит устанавливается в единицу при записи в буфер команды, которой назначено данное значение тега, и сбрасывается после её выполнения (передачи результата в коммутатор). Регистр, образованный Ттах +1 битами (от 0 до Ттах), каждый из которых соответствует одному значению тега, называется памятью занятых тегов. При этом, занятость конкретного і-го значения тега определяется содержимым ВТМ(i).

Управляется регистр указателем  $ifd\_tag$ , значение которого присваивается очередной выбранной команде в качестве тега. В исходном состоянии ВТМ обнулен. Значение указателя  $ifd\_tag$  указывает на начальное значение тега. В нулевой клетке группы оно будет равно нулю, во второй единице, в третьей двойке и т.д. Начиная очередной цикл выборки команд, клетка анализирует содержимое  $BTM(ifd\_tag)$ . Если оно равно '1', то выборка в этой и других клетках группы приостанавливается до тех пор, пока оно не станет равным нулю. Если оно равно '0' во всех клетках группы, то выбранной команде присваивается  $tag:=ifd\_tag$ , которое записывается вместе с ней в буфер. После записи команды в буфер значение BTM(tag) устанавливается в '1', значение  $ifd\_tag$  устанавливается равным  $(ifd\_tag+1)$  mod Tmax и клетка приступает к выбору следу-

ющей команды.

## 3.2.2 Организация буфера команд

Буфер команд – это массив из 1 строк, где

$$m < l < Tmax + 1$$

m - размер окна видимости и состоит из буфера хранения операционной части команды и буфера хранения операндов.

Операционная часть представляет собой прямоадресуемый массив, строки которого кроме кода команды, включает в себя всю необходимую служебную информацию для исполнения команд и рассылки результатов, а именно, тег команды и признаки готовности первого(второго) операнда для выполнения команды.

Строки буфера хранения операндов позиционно привязаны к строкам операционной части и имеет ассоциативную адресацию. Ассоциативным адресом, по которому осуществляется запись запрошенного результата является его тег, который передается в буфер команд при декодировании команды.

В качестве операндов при выполнении операций могут использоваться: запрошенные результаты команд-источников, поступающие из коммутатора; значения, вычисленные при декодировании командного слова, а также непосредственно присутствующие в командном слове или взятые из регистров общего назначения.

В первом случае признак готовности данного операнда при записи команды устанавливают в состояние «не готов», а во втором — в состояние «готов». После получения запрошенного результата от коммутационного устройства, признак, в первом случае, также устанавливают в состояние «готов».

Команда, получившая все операнды, проходит приоритетный отбор среди других готовых команд в буферном устройстве, после чего выдается на исполнение при условии незанятости исполнительного устройства.

Каждый полученный результат вместе с тегом его команды посылают во все коммутационные устройства, которые отбирают по номерам, запрошенные данной клеткой результаты, и передают их в ее буферные устройства в качестве операндов.

#### 3.2.3 Управление коммутационной средой

Каждое коммутационное устройство состоит из двух блоков памяти запросов и блока памяти результатов. Каждый блок памяти запросов представляет собой регистр размером Tmax+1 бит, в котором при запросе результата с тегом ј для использования операнда, в ј-том бите регистра записывают единицу («запрос установлен»), а после выдачи результата с этим тегом в ј-тый бит записывают ноль («запрос снят»). В первом блоке записываются запросы на получение первого операнда, во втором – второго. Запись запросов и последующее решение по выдаче операндов принимаются независимо, т.е. возможна одновременная выдача операндов в буфер команд с различными тегами. Память результатов состоит из Tmax +1 строк, каждая из которых содержит два поля: значения результата; признака готовности результата.

В исходном состоянии признак готовности результата содержит ноль (результата нет). Каждый полученный клеткой результат с его тегом поступает во все коммутационные устройства группы. Каждое коммутационное устройство записывает полученный результат в поле значения результата строки, номер которой соответствует номеру тега и устанавливает в этой строке признак готовности результата в единицу (результат получен).

Строка коммутатора считается готовой выдать результат, если одновременно есть хотя бы один запрос на этот результат и готово его значение. Из всех строк, готовых к выдаче, выбирается строка с самым "старым"результатом и его значение вместе с тегом, равным номеру строки, выдаётся в буфер команд в качестве операнда. Одновременно сбрасывается признак запроса. Признак готовности и поле значения при этом не изменяются. Таким образом, учитывается, что результат может потребоваться командам, декодируемым позже. Сбрасывается признак готовности результата в і-той строке при назначении тега с этим значением новой команде. Необходимым условием этого является выполнение всех запросов на і-тый результат, т.е. і-тые строки первой и второй памяти запросов должны быть нулевые. Иначе процесс выборки и декодирования задерживается до выполнения всех запросов на і-тый результат.

## 3.3 Структура и организация клетки

Основой центрального процессорного устройства мультиклеточного микропроцессора является совокупность процессорных блоков (клеток), объединённых особой коммутационной средой и образующей вычислительное ядро. Структурные связи вычислительного ядра, а также структурная схема центрального процессорного устройства мульти-

клеточного микропроцессора см. на рис.2.

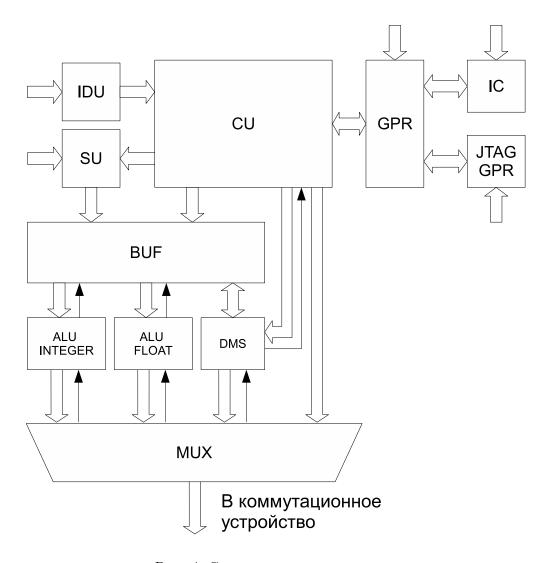

В состав клетки (см на рис.4) входят следующие устройства:

- 1. Устройство выборки команд IDU (Instruction Distribution Unit).

- 2. Устройство управления CU (Control Unit).

- 3. Коммутационное устройство SU (Switch Unit).

- 4. Буфер команд(BUF).

- 5. Целочисленное АЛУ.

- 6. АЛУ с плавающей точкой.

- 7. Блок доступа к памяти данных DMS (Data Memory Service).

- 8. Мультиплексор результатов МUХ.

- 9. Набор регистров GPR (General-Purpose Registers).

- 10. Контроллер прерываний IC (Interrupt Controller).

- 11. Отладочный блок JTAG-GPR.

Мультиклеточный микропроцессор исполняет программу, представляющую собой последовательность параграфов. Параграф — это набор команд, связанных друг с другом зависимостями по данным. Параграфы связаны друг с другом цепочками условных и безусловных переходов, задающих адрес следующего выполняемого параграфа.

#### 3.3.1 Устройство выборки команд

После сигнала сброса все клетки микропроцессора автоматически конфигурируются в единую task—группу и начинают выборку параграфа с начального адреса. При этом устройства выборки команд клеток группы согласованно читают фрагмент памяти программ, содержащий не менее k очередных команд, которые размещаются на регистрах команд клеток, а именно i — тая команда размещается на регистре команд i — той клетки. Размещение команды сопровождается формированием признака готовности команды к декодированию. Выборка команд конвейеризирована. Одновременно, если среди выбранных k команд не было отмеченных управляющим признаком «конец параграфа», в IDU клеток формируются и записываются новые значения регистров адреса, для согласованного чтения следующего фрагмента памяти программ.

Если среди выбранных команд была команда, отмеченная управляющим признаком «конец параграфа», адрес следующего выполняемого параграфа уже вычислен и были выполнены все записи в регистры, то во всех клетках группы новое значение регистра адреса текущего параграфа устанавливается равным адресу следующего выполняемого параграфа, и выборка команд продолжается с нового адреса. Если среди выбранных ко-

Рис. 4: Структурная схема клетки

манд была команда, отмеченная управляющим признаком «конец параграфа», а адрес следующего выполняемого параграфа на этот момент не вычислен, то выборка команд приостанавливается, и возобновляется, когда будет вычислен адрес следующего выполняемого параграфа.

## 3.3.2 Устройство управления

Устройство управления обеспечивает декодирование команды, ее запись в буфер команд, либо непосредственно на исполнение, а также формирование (при необходимости) запроса коммутационному устройству на получение результатов ранее выбранных команд.

В каждой клетке, при декодировании, каждой очередной выбранной команде присваивается очередное значение тега. Значение очередного тега формируется клетками син-

www.multiclet.com UM HDL50002 Rev: 101 09.07.2015 22-172

хронно и изменяется циклически от 0 до Ттах.

Присвоенное значение тега сопровождает команду на всех этапах её выполнения и присваивается результату её выполнения. Если значение тега присвоено команде и результат её выполнения не получен коммутационным устройством, либо получен, но пока не выдан потребителям, то это значение тега считается занятым.

По значению тега команды и значениям её ссылок формируются теги запрашиваемых результатов для формирования первого и второго операндов команды-приёмника. Эти теги используются для формирования запроса коммутационному устройству на результаты и в качестве ассоциативного адреса при записи их значения в требуемую строку буфера команд. В последнем случае они записываются в буфер, вместе с кодом операции и ее тегом, как значения операндов, сопровождаемые нулевым признаком готовности операнда («не готов»). Если результаты не запрашиваются, а значения операндов берутся из регистров или непосредственно из командного слова, то их значения записываются в буфер команд с признаком готовности операнда равным единице («готов»).

Одновременно в клетке формируется и передаётся в устройство выборки команд сигнал готовности клетки к приёму следующей команды. Формирование сигнала приостанавливается, если хотя бы в одной клетке группы:

- 1. Значение тега занято;

- 2. Установлен режим контроля очередности чтения/записи, а декодируемая команда команда чтения и в буфере есть не выполненные команды чтения предыдущего параграфа;

- 3. Установлен режим контроля очередности чтения/записи, а декодируемая команда команда записи и в буфере есть не выполненные команды записи предыдущего параграфа;

- 4. В буфере команд есть свободное место.

В ряде случаев устройство управления может самостоятельно выполнить команду без помещения ее в буфер в команд:

- 1. Если выбранная команда чтение регистра.

- 2. Если для выбранной команды требуется только константа и/или значение регистра ( команды SET, GET, JMP или IRM).

- 3. Если выбранная команда чтение из памяти по известному адресу, содержащемуся в константе и/или регистре, и блок DMS не занят.

Также устройство управления может самостоятельно выполнять обращение к блоку

DMS, если декодированная инструкция использует косвенную адресацию аргумента, и блок DMS не занят.

Если текущая конфигурация микропроцессора предусматривает несколько task-групп, то каждая task-группа работает независимо. При этом каждая task-группа имеет независимый набор регистров общего назначения и индексных регистров, а клетки внутри группы работают так же, как было описано выше.

Изменение текущей конфигурации процессора возможно только после выполнения всех команд текущего параграфа. Для задания конфигурации, отличных от конфигурации по умолчанию, сначала устанавливается в «1» бит 7 (бит разрешения реконфигурации) и бит 8 (бит признака очистки буферов) регистра PSW. Далее мультиклеточный микропроцессор будет функционировать следующим образом:

- 1. Текущий параграф («параграф 1») продолжит выполняться со «старым» значением PSW.

- 2. Фактическое значение PSW обновится (т.е. установятся биты 7 и 8) только при переходе на следующий параграф («параграф 2»).

- 3. Внутри параграфа 2 программа должна установить новые значения регистров конфигурации процессора (ICR, PSW и NEWADDR).

- 4. Поскольку установлен бит 8 регистра PSW, выполнение параграфа 2 не завершится, пока не не будут выполнены все команды, находящиеся в буферах.

- 5. По завершении параграфа 2 регистры конфигурации принимают значения, заданные программой, и формируется новый набор task-групп.

- 6. Каждая task-группа, работая независимо, начинает выполнение программы со «своего» адреса, заданного ей через регистр NEWADDR.

При изменении конфигурации клеток процессора они могут объединяться в одну группу (композиция), либо разбиваться по группам. При композиции клеток одна из групп является «ведущей», т.е. исполняемая ей программа «присоединяет» клетки к данной группе. При этом программы, исполняемые task-группами, должны быть построены таким образом, чтобы в момент композиции все присоединяемые task-группы были остановлены (например, с помощью параграфа, не содержащего инструкций перехода).

#### 3.3.3 Буфер команд

Декодированная команда записывается в строку буфера кода операции буферного устройства, для этой строки формируется признак «занято». В буфер соответствующего операнда буферного устройства, если значение операнда известно, записывают его зна-

чение, устанавливают в состояние «да» признак готовности операнда, иначе в массив тегов операнда записывается тег результата выполнения команды, который был запрошен в качестве операнда, признак готовности операнда устанавливают в состояние «нет». Если из коммутационного устройства (для первого операнда) или из коммутационного устройства (для второго операнда) в качестве операнда приходит результат выполнения команды с запрошенным тегом (этот тег совпадает с тегом, записанным в массив тегов операнда), то этот результат записывается в буфер операнда буферного устройства в строку, номер которой совпадает с номером строки буфера кода операции буферного устройства, в которую был записан код операции соответствующей команды. Команда передается на исполнение если:

- 1. Известны значения всех необходимых операндов.

- 2. Соответствующее исполнительное устройство готово к приёму команды.

- 3. В буферном устройстве нет более приоритетных (более «старых») команд, готовых к выполнению.

В буферном устройстве формируется и выдаётся устройству управления сигнал готовности буферного устройства к записи декодируемой команды, имеющий два состояния «да» и «нет», указывающие на его готовность, анализируются коды операций команд, находящихся в буферном устройстве, и формируют сигналы наличия команд чтения и записи, которые имеют два состояния «да» и «нет», указывающие на наличие или отсутствие соответствующих команд в буферном устройстве. Эти сигналы выдаются в мультиклеточный процессор, где одноименные сигналы, полученные от всех клеток объединяют схемами ИЛИ и формируют, соответственно, общие сигналы наличия команд чтения и записи. Очерёдность выполнения команд внутри параграфа подчиняется следующим правилам:

- 1. Если включён контроль очерёдности чтения/записи, выполнение команд записи не начнётся, пока не завершится выполнение всех команд чтения в текущем параграфе, а выполнение команд чтения не начнется, пока не будут выполнены все команды записи предыдущих параграфов.

- 2. При выполнении команд записи в регистры общего назначения, индексные и служебные регистры, записываемые значения помещаются в регистры только по окончании декодирования всех команд текущего параграфа, и перед выборкой команд следующего параграфа. Следует заметить, что адрес следующего параграфа также хранится в одном из служебных регистров (NEWADDR), с аналогичной логикой работы.

- 3. При выполнении команд записи в периферийные регистры, записываемые значения помещаются в регистры непосредственно в момент выполнения команды.

- 4. Во всех других случаях очерёдность выполнения команд определяется исключитель-

но готовностью значений аргументов команд, готовностью исполнительных устройств клетки и наличием других («более старых») готовых команд.

#### 3.3.4 Коммутационное устройство

Состав и функционирование коммутационного устройства изложены в разделах выше.

#### 3.3.5 Целочисленное АЛУ

Целочисленное АЛУ предназначено для выполнения команд над целочисленными операндами, при этом операнды могут быть представлены в следующих форматах (в зависимости от команды):

64-битные;

32-битные;

16-битные;

8-битные;

упакованные 32-битные;

упакованные 16-битные.

Структурно целочисленное АЛУ состоит из двух частей:

умножитель – конвейеризированный блок, предназначенный для выполнения команды умножения;

вычислитель – неконвейеризированный блок, предназначенный для выполнения всех остальных команд из набора команд над целочисленными операндами.

## 3.3.6 АЛУ с плавающей точкой

АЛУ с плавающей точкой предназначено для выполнения команд над операндами, представленными в формате чисел с плавающей запятой одинарной (32 бита) или двойной точности (64 бита) в соответствии с требованиями стандарта IEEE-754. Структурно АЛУ с плавающей точкой состоит из трёх частей:

1. делитель одинарной точности – блок, предназначенный для выполнения команд деления и извлечения квадратного корня над операндами, представленными в формате чисел с плавающей точкой одинарной точности;

- 2. делитель двойной точности блок, предназначенный для выполнения команд деления и извлечения квадратного корня над операндами, представленными в формате чисел с плавающей точкой двойной точности;

- 3. вычислитель FASM блок, предназначенный для выполнения остальных команд из набора команд над операндами, представленными в формате чисел с плавающей точкой одинарной или двойной точности.

АЛУ с плавающей точкой аппаратно оптимизирован для выполнения команд комплексного умножения операндов, представленных в формате чисел с плавающей точкой одинарной точности. Оптимизация достигается за счёт одновременного выполнения операций умножения и сложения, входящих в состав команды комплексного умножения.

Делители одинарной и двойной точности — неконвейеризированные, поэтому, АЛУ с плавающей точкой не может принять на выполнение следующую команду деления или извлечения квадратного корня, пока не будет выполнена предыдущая.

Вычислитель FASM – конвейеризированный, поэтому, может принимать на выполнение следующую команду на каждом следующем такте.

#### 3.3.7 Блок доступа к памяти данных

#### 3.3.8 Мультиплексор результатов

Обеспечивает приоритетную выдачу результатов в коммутационные устройства, если одновременно готовы результаты выполнения команд целочисленного АЛУ, АЛУ с плавающей точкой, DMS, либо результат получен непосредственно из устройства управления. По приоритету выдачи результата исполнительные устройства распределяются следующим образом:

- 1. Устройство управления;

- 2. АЛУ с плавающей точкой;

- 3. DMS;

- 4. Целочисленное АЛУ.

Исполнительные устройства, результат работы которых на текущем такте не может быть выдан в коммутационное устройство, записывают результат выполнения команды в выходной регистр и ожидают своей очереди на выдачу результата.

## 3.3.9 Набор регистров

В состав каждой клетки входит свой набор регистров (управляющие (служебные), индексные и регистры общего назначения). Наборы регистров клеток, входящих в одну task-группу, объединяются в единую группу, при этом чтение и запись в одинаковые регистры разных клеток происходят идентично. Со стороны центрального процессорного устройства это выглядит, как наличие у task-группы одного набора регистров (как у одной клетки). При изменении конфигурации соответственно происходит перегруппировка наборов регистров клеток.

В состав каждой клетки входит свой блок регистров (GPR), включающий:

- набор регистров общего назначения,

- набор индексных регистров,

- регистр управления микропроцессора PSW,

- регистр адреса возврата из прерываний IRETADDR,

- регистр принудительного запуска прерываний FORCE,

- регистр адреса обработчика прерываний IHOOKADDR,

- регистр модификации индексных регистров REGMOD,

- регистр адреса текущего параграфа CURRENTADDR,

- регистр адреса следующего параграфа NEWADDR,

- регистр предыдущего значения PSW LASTPSW,

- регистр конфигурации ICR.

Кроме указанных выше регистров, блок GPR имеет в своём составе интерфейс системных регистров мультиклеточного процессора. В следующих разделах имеется более подробное описание регистров.

#### 3.3.10 Контроллер прерываний и отладочный блок

Подробно описываются в следующих разделах.

## 3.4 Регистры

Все регистры, кроме системных, имеют ширину 64 бита. Чтение/запись регистров происходит с помощью специализированных команд.

РОН, индексные регистры и управляющие регистры имеют копии в каждой клетке. Эта особенность является необходимостью, т.к. при реконфигурации необходимо иметь набор регистров в каждой клетке. Системные регистры находятся в устройствах, таких как системный таймер, PLL и т.д. Это разделяемые ресурсы МП.

| №       | Название                          | Примечание                                                 |

|---------|-----------------------------------|------------------------------------------------------------|

|         | РОН, инде                         | ксные регистры (дублируются в каждой клетке)               |

| 0-7     | нет                               | регистры общего назначения (РОН)                           |

| 8-15    | нет                               | индексные регистры                                         |

|         | Системные регистры                | (существуют в одном экземпляре в системных устройствах)    |

| 16      | PLLCR                             | регистр управления генератором                             |

| 17      | PLLSTR                            | регистр состояния генератора                               |

| 18      | PLLTMCR                           | регистр управления модулем коммутации системы тактирования |

| 19      | SWCH0_CTRL                        | управления каналом памяти 0                                |

| 20      | SWCH1_CTRL                        | управления каналом памяти 1                                |

| 21      | SWCH2_CTRL                        | управления каналом памяти 2                                |

| 22      | SWCH3_CTRL                        | управления каналом памяти 3                                |

| 23      | ST0PRDR                           | период системного таймера 0                                |

| 24      | ST1PRDR                           | период системного таймера 1                                |

| 25      | ST2PRDR                           | период системного таймера 2                                |

| $^{26}$ | ST3PRDR                           | период системного таймера 3                                |

| 27      | ST0CR                             | регистр управления таймера 0                               |

| 28      | ST1CR                             | регистр управления таймера 1                               |

| $^{29}$ | ST2CR                             | регистр управления таймера 2                               |

| 30      | ST3CR                             | регистр управления таймера 3                               |

| 31      | зарезервировано                   |                                                            |

| 32      | ST0VAL                            | текущее значение таймера 0                                 |

| 33      | ST1VAL                            | текущее значение таймера 1                                 |

| 34      | ST2VAL                            | текущее значение таймера 2                                 |

| 35      | ST3VAL                            | текущее значение таймера 3                                 |

| 36-38   | зарезервировано                   |                                                            |

| 39      | DTC_STEP_INDX                     | регистр управления инкрементацией адресов DTC              |

| 40      | DTC_CTRL                          | регистр управления DTC                                     |

| 41      | DTC_ST                            | регистр состояния DTC                                      |

| 42      | $\mathrm{DTC}_{-}\mathrm{IMASK0}$ | регистр маски 0 DTC                                        |

| 43      | DTC_IMASK1                        | регистр маски 1 DTC                                        |

| 44      | DTC_DATA                          | регистр данных DTC                                         |

| 45      | DTC_S_ADDR                        | адрес источника                                            |

| 46      | DTC_D_ADDR                        | адрес приёмника                                            |

| 47      | ROM_CTRL                          | регистр управления и статуса внешнего ПЗУ                  |

|         | Управлян                          | ощие регистры (дублируются в каждой клетке)                |

| 48      | PSW                               | регистр управления процессором                             |

| 49      | INTR                              | регистр прерываний                                         |

| 50      | MSKR                              | регистр маски прерываний                                   |

| 51      | ER                                | регистр ошибок                                             |

| 52      | IRETADDR                          | регистр адреса возврата из прерываний                      |

| 53      | FORCE                             | регистр принудительного запуска прерываний                 |

| 54      | зарезервировано                   |                                                            |

| 55      | IHOOKADDR                         | адрес обработчика прерываний                               |

| 56      | INTNUM                            | регистр номера прерывания                                  |

| 57      | REGMOD                            | регистр модификации индексных регистров                    |

| 58      | зарезервировано                   |                                                            |

| 59      | CURRENTADDR                       | регистр адреса текущего параграфа                          |

| 60      | NEWADDR                           | регистр адреса следующего параграфа                        |

| 61      | LASTPSW                           | регистр предыдущего значения PSW                           |

| 62      | DFADDR                            | регистр аварийного перехода                                |

| 63      | ICR                               | регистр информационной связанности                         |

Таблица 4: Регистры процессора

## 3.5 Контроллер прерываний

Контроллер прерываний входит в состав каждой клетки. В МП контроллеры прерывания работают как один в выделенной группе клеток. В группе клеток контроллеры прерываний не могут быть разделены или сконфигурированы отдельно. Система прерываний МП допускает обработку 44 прерываний. Источник с номером «0» имеет наивысший приоритет при обработке прерываний.

## Структура прерываний

Прерывания можно условно разделить на две группы: системные прерывания и прерывания от периферии. Системные прерывания занимают адреса с 0 по 15 в контроллере прерываний и являются более приоритетными по сравнению с прерывания от периферии. Системные прерывания с номерами с 0 по 4 являются немаскируемыми. Прерывания от периферии занимают адреса с 16 по 63.

| 0  | II (DATA41)                                        |

|----|----------------------------------------------------|

| 0  | Немаскируемое внешнее прерывание (ENMI)            |

| 1  | зарезервировано                                    |

| 2  | Немаскируемое исключение в аппаратной части (PERE) |

| 3  | Немаскируемое программное исключение (PRGE)        |

| 4  | зарезервировано                                    |

| 5  | зарезервировано                                    |

| 6  | Маскируемое прерывание - внешний сигнал wake_up    |

| 7  | Маскируемое прерывание от контроллера транзакций   |

| 8  | Маскируемое прерывание от системного таймера (ST0) |

| 9  | Маскируемое прерывание от системного таймера (ST1) |

| 10 | Маскируемое прерывание от системного таймера (ST2) |

| 11 | Маскируемое прерывание от системного таймера (ST3) |

| 12 | Маскируемое программное прерывание (SW0)           |

| 13 | Маскируемое программное прерывание (SW1)           |

| 14 | Маскируемое программное прерывание (SW2)           |

| 15 | Маскируемое программное прерывание (SW3)           |

| 16 | Маскируемое прерывание от ADC0                     |

| 17 | Маскируемое прерывание от DAC0                     |

| 18 | Маскируемое прерывание от ADC1                     |

| 19 | Маскируемое прерывание от DAC1                     |

| 20 | Маскируемое прерывание от UART0                    |

| 21 | Маскируемое прерывание от UART1                    |

| 22 | Маскируемое прерывание от UART2                    |

| 23 | Маскируемое прерывание от UART3                    |

| 24 | Маскируемое прерывание от I2C0                     |

| 25 | Маскируемое прерывание от I2C1                     |

| 26 | Маскируемое прерывание от SP10                     |

| 27 | Маскируемое прерывание от SPI1                     |

| 28 | Маскируемое прерывание от I2S0                     |

| 29 | Mаскируемое прерывание от GPTIM0                   |

|    | ı                                                  |

| 30 | Mаскируемое прерывание от GPTIM1    |

|----|-------------------------------------|

| 31 | Mаскируемое прерывание от GPTIM2    |

| 32 | Mаскируемое прерывание от GPTIM3    |

| 33 | Маскируемое прерывание от WDT       |

| 34 | Маскируемое прерывание от RTC       |

| 35 | Mаскируемое прерывание от GPIOA     |

| 36 | Mаскируемое прерывание от GPIOB     |

| 37 | Mаскируемое прерывание от GPIOC     |

| 38 | Mаскируемое прерывание от GPIOD     |

| 39 | Mаскируемое прерывание от GPIOE     |

| 40 | Mаскируемое прерывание от GPIOF     |

| 41 | Mаскируемое прерывание от ETHERNET0 |

| 42 | Маскируемое прерывание от USB0      |

| 43 | Маскируемое прерывание от USB0_EPI  |

| 44 | Маскируемое прерывание от USB0_EPO  |

| 45 | Маскируемое прерывание от PWM0      |

| 46 | Маскируемое прерывание от STAT      |

|    |                                     |

| 63 |                                     |

## 3.5.1 Структура контроллера прерываний

Рис. 5: Блок-схема контроллера прерываний

Контроллер прерываний выполняет следующие функции:

- определяет самое приоритетное прерывание на каждом такте и формирует его номер на шине INTNUM;

- обрабатывает информацию об аппаратных и программных сбоях, формирует запрос обработки прерывания, если возникло что-то из перечисленного.

Из клетки на контроллер прерываний приходят 4 сигнала об ошибках в ходе выполнения программы, по которым в обработчике исключений формируется сигнал PRGE:

- II выбрана несуществующая инструкция;

- OV возникло переполнение при попытке разделить на 0 в блоке операций с числами с плавающей запятой;

- ISQRT попытка взять корень из отрицательного числа в блоке операций с числами с плавающей запятой;

- FNAN в ходе операции с числами с плавающей запятой или на входе блока операций с числами с плавающей запятой возникло число = NAN.

С шины периферийных устройств на обработчик исключений поступают сигналы HRESP, состояние линий которых говорит об ошибках или их отсутствии при обращении по шине. При наличии ошибки формируется сигнал PERE.

Так же каждая клетка формирует сигнал int\_st - прерывание от системного таймера. и SWI - программно-формируемое прерывание. С шины периферийных устройств при-

ходят сигналы запроса прерывания от каждого периферийного устройства. С вводов/выводов МП приходят сигналы /enmi – внешнее немаскируемое прерывание и wake\_up - сигнал вывода МП из «спящего» режима внешней системой.

#### 3.5.2 Регистры контроллера прерываний

Для работы системы прерывания и функционирования программ обработки прерываний имеются следующие регистры:

| Регистр            | Доступ | Описание                                |

|--------------------|--------|-----------------------------------------|

| INTR               | RW     | Регистр прерываний                      |

| MSKR RW Регистр ма |        | Регистр маски прерываний                |

| FORCE              | W      | Регистр установки прерывания            |

| INTNUM             | R      | Регистр номера выработанного прерывания |

| ER                 | R      | Регистр ошибок                          |

Все регистры имеют разрядность 64 бита. Номера бит во всех регистрах кроме INTNUM и ER, которые имеет другую структуру, соответствуют номерам прерываний.

## Регистр INTR.

Доступен как для чтения, так и для записи. Запись 1 в какие-либо биты данного регистр произведет сброс соответствующих бит данного регистра в 0. Данный регистр является регистром защелкой, и он захватывает пришедшие на его вход данные до тех пор, пока не будет сброшен записью 1 в соответствующие биты.

| INTR       | Регистр прерываний |      |  |

|------------|--------------------|------|--|

| Номер бита | 63 47              | 46 0 |  |

| Описание   | зарезервировано    | INTR |  |

$63 \dots 47$  зарезервировано

46 ... 0 номер выработанного прерывания

## Регистр MSKR.

Регистр MSKR доступен как для чтения, так и для записи. Для разрешения прерываний с определенными номерами, необходимо выставить в 1 соответствующие биты данного регистра. Биты 0-3 являются немаскируемыми.

| MSKR       | Регистр маски прерываний |      |                 |

|------------|--------------------------|------|-----------------|

| Номер бита | 63 47                    | 46 4 | 30              |

| Описание   | зарезервировано          | MSKR | зарезервировано |

63 ... 47 зарезервировано

46 ...4 номер маскируемого прерывания

3 ...0 зарезервировано

#### Peructp FORCE.

Регистр FORCE доступен только для записи. Запись 1 в какие-либо биты данного регистра сформируют единичный импульс на вход регистра прерываний, что в свою очередь вызовет установку соответствующих бит в регистре INTR. На следующем такте после записи 1 в какие-либо биты данного регистра, все биты данного регистра будут сброшены в 0.

| FORCE      | Регистр устано  | вки прерываний |

|------------|-----------------|----------------|

| Номер бита | 63 47           | 46 0           |

| Описание   | зарезервировано | FORCE          |

63 ... 47 зарезервировано

46 ... 0 номер принудительного прерывания

#### Регистр INTNUM.

Регистр INTNUM доступен только для чтения, данный регистр содержит номер самого приоритетного прерывания, среди тех, что ждут обработки в данный момент.

| INTNUM     | Регистр управл  | ения каналом коммутатора |

|------------|-----------------|--------------------------|

| Номер бита | 63 6            | 5 0                      |

| Описание   | зарезервировано | INTNUM                   |

63 ... 6 зарезервировано

5 ... 0 номер самого приоритетного прерывания на момент чтения регистра

#### Регистр ЕR.

Регистр ER доступен только для чтения, данный регистр содержит информацию о программных или аппаратных сбоях. Во всех битах регистра '1' является признаком возникновения события.

| ER          | Регист | р управа | тень         | ія ка | нало | м комм  | утатора  |

|-------------|--------|----------|--------------|-------|------|---------|----------|

| Номер бита  | 63 7   | 6 5      | 4            | 3     | 2    | 1       | 0        |

| Описание    | _      | HRESP    | II           | OV    | _    | ISQRT   | FNAN     |

| 637         | _      | ě        | заре         | езерв | upc  | вано    |          |

| $6 \dots 5$ | HRE    | SP o     | оши          | бка   | прі  | и обраг | цении п  |

|             |        | 5        | вл           | тотс  | яп   | ризнак  | ом нали  |

| 4           | II     | I        | зыб          | рана  | не   | сущест  | вующая   |

| 3           | ov     | I        | 303E         | икл   | о п  | ереполн | ение пр  |

|             |        | I        | още          | ей за | гип  | гой     |          |

| 2           | _      | ě        | $ap\epsilon$ | гзерв | upc  | вано    |          |

| 1           | ISQI   | RT 1     | юп           | ытка  | в3.  | ять кор | ень из   |

|             |        | 3        | запя         | нтой  |      |         |          |

| 0           | FNA    | N i      | зхс          | де о  | пер  | ации с  | числам   |

|             |        | (        | спл          | аван  | още  | ей запя | гой возі |

#### 3.5.3 Порядок обработки прерываний

В случае возникновения события, вызывающего запрос на обработку прерывания, оно фиксируется в регистре INTR. Регистр MSKR является фильтром, который допускает или нет сигналы из регистра INTR к дальнейшей обработке. После регистра MSKR сигналы попадают в схему определения приоритета, где происходит определение самого приоритетного прерывания в данном такте, его номер заносится в регистр INTNUM. На выходе контроллера прерывания сигнал int переходит в активное состояние. Клетка фиксирует активный уровень сигнала запроса обработки прерывания. Переход в обработчик прерывания происходит в конце параграфа, когда завершаются все записи в память и регистры, если таковые были в параграфе.

Адрес начального обработчика прерываний находится в регистре IHOOKADDR. Ядро работает только с одним адресом перехода на обработчик прерываний. По этому адресу может находится любой алгоритм на усмотрение пользователя. Определение порядка работы с конкретным запросом прерывания возложено на программиста.

Латентность времени перехода на обработчик прерывания имеет зависимость от программы пользователя. Рекомендуется перед стартом программы очистить регистр INTR записью 1 во все биты регистра.

Важно заметить, что для каждой группы клеток можно задавать обработчик прерываний в регистре IHOOKADDR, задавать MSKR, т.к. у каждой группы клеток появляется свой набор этих регистров.

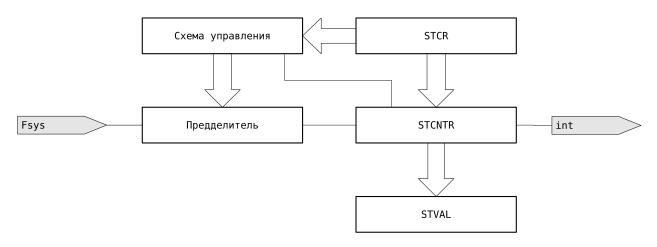

## 3.6 Системный таймер

Системный таймер предназначен для формирования заданных периодических или однократных временных интервалов. Таймер представляет собой инкрементирующий счетчик с делителем тактового сигнала на входе. Конечное значение счетчика записывается в регистр периода таймера, управление осуществляется через регистр STxCR, счет начинается с нуля. По истечении заданного временного интервала формируется запрос на обработку прерывания.

Рис. 6: Блок-схема системного таймера

На рис.6 изображена блок-схема таймера. Ниже приведены формулы для расчета частоты и периода интервалов, формируемых системным таймером. Значения PREDIV и CNTVAL задаются в регистрах STxCR и STxPRDR соответственно.

• период формируемого интервала:

$$T = T_{clk} \cdot (PREDIV + 1) \cdot (CNTVAL + 1);$$

• частота следования временных интервалов:

$$F = \frac{F_{clk}}{(PREDIV + 1) \cdot (CNTVAL + 1)};$$

#### 3.6.1 Режимы работы

• Однократное формирование временного интервала – таймер запускается пользователем (в бит STxCR(EN)='1'), а по достижении счетчиком таймера значения,

www.multiclet.com UM HDL50002 Rev: 101 09.07.2015 38-172

заданного в регистре периода таймера, таймером выдается запрос на обработку прерывания, после этого бит STxCR(EN) устанавливается в '0', и таймер останавливается до следующей записи значения '1' в STxCR(EN);

• Периодическая генерация временных интервалов – таймер запускается и останавливается пользователем (в бит STxCR(EN) записывается соответствующее значение). По достижении счетчиком таймера значения, заданного в регистре периода таймера, таймером выдается запрос обработки прерывания, счетчик перезагружается значением '0', и работа таймера продолжается до того, как пользователь запишет значение '0'в бит STxCR(EN).

При записи в регистр STxPRDR новое значение периода будет установлено и счетчик начнет считать с нуля. При записи в STxCR(PREDIV) новое значение предделителя будет загружено и счетчик начнет считать с нуля. Настоятельно рекомендуется перед изменением режима работы таймера сначала остановить его, записав STxCR(EN)='0', потом задать новые значения в регистре STxCR. Режим работы системного таймера устанавливается в STxCR(MD). Доступно 4 системных таймера: ST0, ST1, ST2, ST3.

| STxPRDR             | Пе | риод                                                                                 | цси | стем | ног | таі | імер | a |  |  |  |  |  |   |      |    |  |  |  |  |  |  |  |  |  |

|---------------------|----|--------------------------------------------------------------------------------------|-----|------|-----|-----|------|---|--|--|--|--|--|---|------|----|--|--|--|--|--|--|--|--|--|

| Номер бита          | 31 | 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 1 0 |     |      |     |     |      |   |  |  |  |  |  |   |      |    |  |  |  |  |  |  |  |  |  |

| Начальное состояние |    | _                                                                                    |     |      |     |     |      |   |  |  |  |  |  |   |      |    |  |  |  |  |  |  |  |  |  |

| Описание            |    |                                                                                      |     |      |     |     |      |   |  |  |  |  |  | I | PERI | OD |  |  |  |  |  |  |  |  |  |

0-31 PERIOD Период системного таймера

| STxCR               | Pe | гист    | руп                                                                                | рав | лени | ясь | істе: | мноі | о та | йме | ра |      |     |  |  |  |   |  |  |  |  |   |   |  |    |    |

|---------------------|----|---------|------------------------------------------------------------------------------------|-----|------|-----|-------|------|------|-----|----|------|-----|--|--|--|---|--|--|--|--|---|---|--|----|----|

| Номер бита          | 31 | 30      | 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |     |      |     |       |      |      |     |    |      |     |  |  |  |   |  |  |  |  |   |   |  |    |    |

| Начальное состояние |    | 0 - 0 0 |                                                                                    |     |      |     |       |      |      |     |    |      |     |  |  |  | 0 |  |  |  |  |   |   |  |    |    |

| Описание            |    |         |                                                                                    |     |      |     |       |      |      |     | I  | PREI | OIV |  |  |  |   |  |  |  |  | _ | _ |  | MD | EN |

| 0    | EN     | Разрещение работы системного таймера ('0'- запрещено, '1'- разрешено) |

|------|--------|-----------------------------------------------------------------------|

| 1    | MD     | Выбор режима работы таймера ('0'- однократный, '1'- многократный)     |

| 2-7  | _      | зарезервировано                                                       |

| 8-31 | PREDIV | Предделитель системного таймера                                       |

| STxVAL              | Te | кущ | ее зі | наче | ние | сист | емн | ого | тайг | иера | ì  |    |    |    |      |    |    |    |    |    |    |    |   |   |   |   |   |   |   |     |     |  |

|---------------------|----|-----|-------|------|-----|------|-----|-----|------|------|----|----|----|----|------|----|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|-----|--|

| Номер бита          | 31 | 30  | 29    | 28   | 27  | 26   | 25  | 24  | 23   | 22   | 21 | 20 | 19 | 18 | 17   | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 1 | L C |  |

| Начальное состояние |    |     |       |      |     |      |     |     |      |      |    |    |    |    | 0    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |     |     |  |

| Описание            |    |     |       |      |     |      |     |     |      |      |    |    |    |    | VALU | JΕ |    |    |    |    |    |    |   |   |   |   |   |   |   |     |     |  |

0-31 VALUE Текущее значение системного таймера

www.multiclet.com UM HDL50002 Rev: 101 09.07.2015 39 - 172

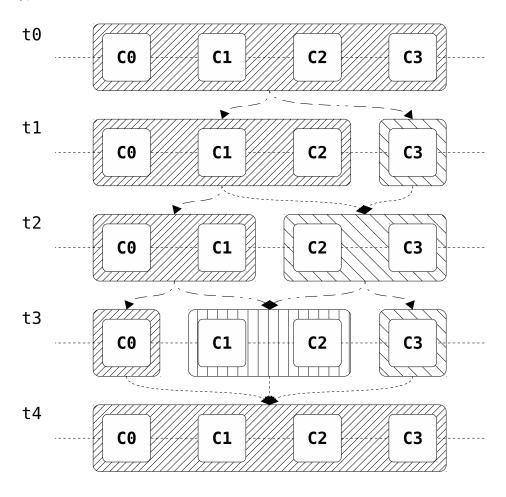

# 4 Средства динамической реконфигурации

Код для мультиклеточного ядра не зависит от количества клеток, которыми он будет исполняться, вычислительные ресурсы мультиклеточного ядра можно распределять во время работы, управление происходит программно. Способность мультиклеточной архитектуры перераспределять свои ресурсы называется — динамической реконфигурацией. Например, клетки мультиклеточного ядра могут быть, как угодно распределены для выполнения какого-либо алгоритма или его части. Группа - это часть клеток мультиклеточного ядра, которые связаны между собой для выполнения какого-либо или части алгоритма независимо от других клеток. В группе может находиться 1 и более клеток. Когда мультиклеточное ядро разделяет группу на части - это называется декомпозиция. Процесс объединения в группу - композиция. На рис. 7 показано как 4-х клеточное ядро со временем реконфигурируется (пример). Клетки, выполняющие одну задачу, имеют одно цветовое заполнение.

Рис. 7: Распределение вычислительных ресурсов